My first car was a used 1971 Volvo 142 and probably did not contain more than a handful of transistors. I used to joke that it could easily survive the EMP from a nuclear explosion. Now, of course, cars contain dozens or more processors, DSP’s and other chips containing millions of transistors. It’s widely expected that the number … Read More

Tag: efpga

Processing Power Driving Practicality of Machine Learning

Despite their recent rise to prominence, the fundamentals of AI, specifically neural networks and deep learning, were established as far back as the late 50’s and early 60’s. The first neural network, the Perceptron, had a single layer and was good certain types of recognition. However, the Perceptron was unable to learn how to… Read More

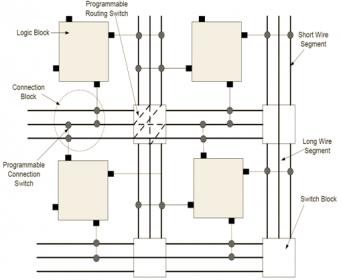

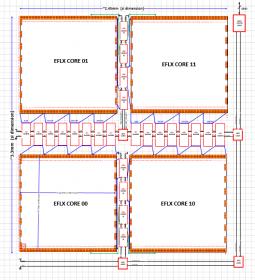

The hierarchical architecture of an embedded FPGA

The most powerful approach to managing the complexity of current SoC hardware is the identification of hierarchical instances with which to assemble the design. The development of the hierarchical design representation requires judicious assessment of the component definitions. The goals for clock distribution, power … Read More

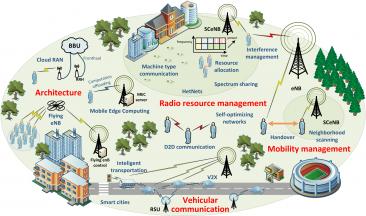

Increased Processing Power Moves to Edge

Recently there has been a lot of buzz about 5G networks. Aside from the talk about it possibly being nationalized, 5G will be a lot different than its predecessors. Rather than a single data link in a predetermined band, 5G will consist of a web of connections all working together to support existing types of data traffic and many new… Read More

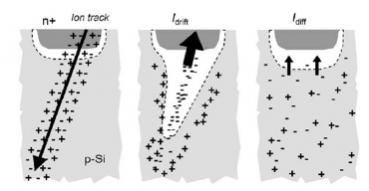

Adapting an embedded FPGA for Aerospace Applications

The IC industry is commonly divided into different market segments – consumer, mobile, industrial, commercial, medical, automotive, and aerospace. A key differentiation among these segments is the characterization and reliability qualification strategy for the fabrication process and design circuitry. For each segment,… Read More

Moving from FPGA’s to Embedded FPGA Fabric – How it’s Done

Buying IP is just a little bit more complicated than buying a pair of shoes. A lot of IP is configurable and requires attention to various design and configuration parameters. We live in an age where commercial soft IP is used pretty often in designs, so people have developed increasing comfort in the process that is required to achieve… Read More

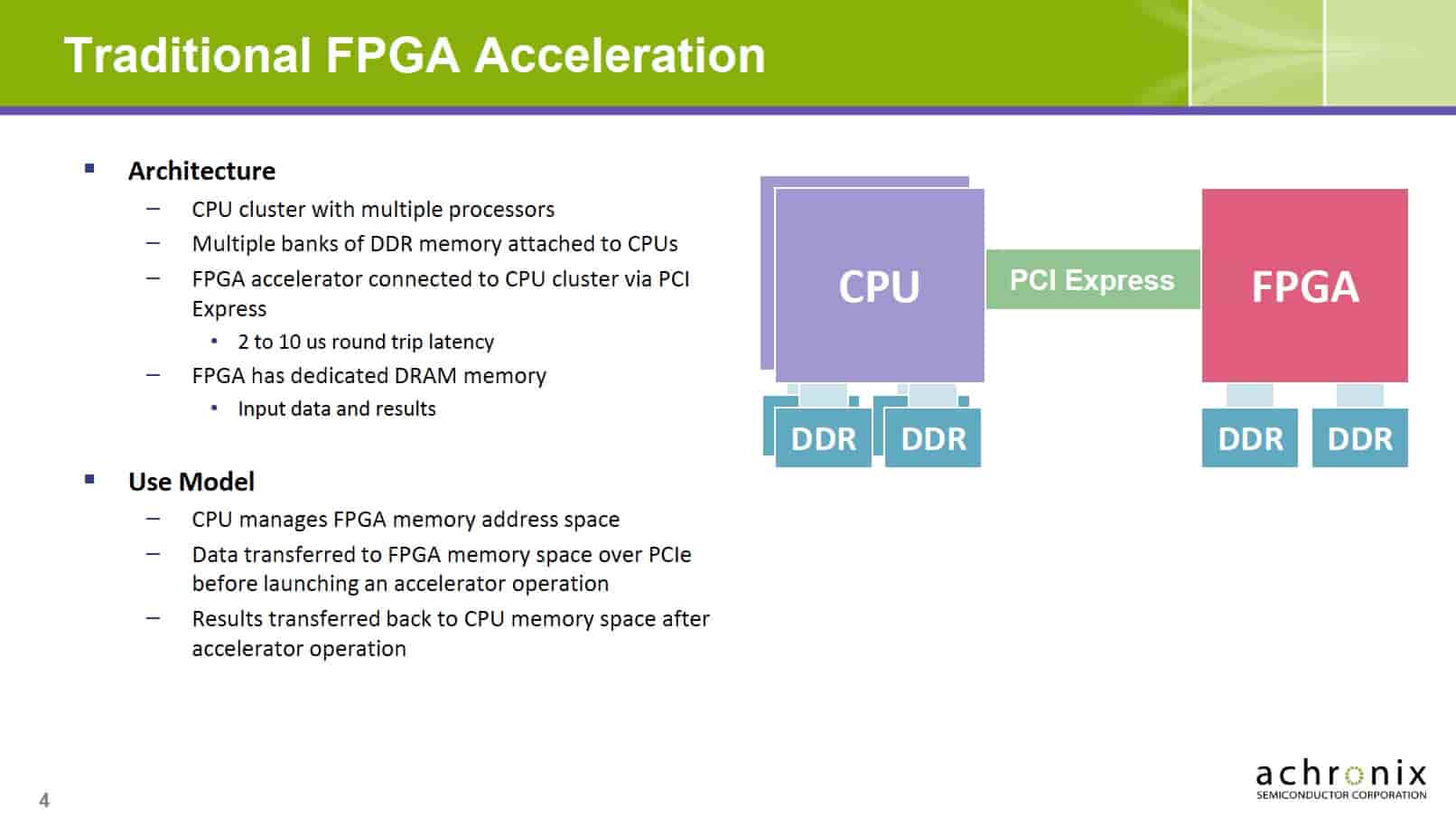

The lofty rise of the lowly FPGA

FPGA programmable logic has served in many capacities since it was introduced back in the early 80’s. Recently, with designers looking for innovative ways to boost system performance, FPGA’s have moved front and center. This initiative has taken on new urgency with the slowing down of process node based performance gains. The… Read More

"The Year of the eFPGA" 2017 Recap

This past January, I had postulated that 2017 would be the “Year of the Embedded FPGA”, as a compelling IP offering for many SoC designs (link). As the year draws to a close, I thought it would be interesting to see how that prediction turned out.

The criteria that would be appropriate metrics include: increasing capital investment;… Read More

The perfect pairing of SOCs and embedded FPGA IP

In life, there are some things that just go together. Imagine the world without peanut butter and jelly, eggs and potatoes, telephones and voicemail, or the internet and search engines. In the world of computing there are many such examples – UARTS and FIFO’s, processor cores and GPU’s, etc. Another trait all these things have is… Read More

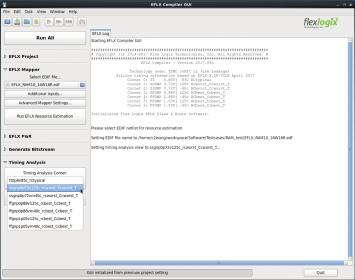

Timing Analysis for Embedded FPGA’s

The initial project planning for an SoC design project faces a difficult engineering decision with regards to the “margin” that should be included as part of timing closure. For cell-based blocks, the delay calculation algorithms within the static timing analysis (STA) flow utilize various assumptions to replace… Read More