I met with Jay Madiraju of Mentor Graphics on Wednesday at DAC to get an update on their AMS simulation products. We worked together at Mentor back when Mach TA was being developed as a Fast SPICE circuit simulator.… Read More

Tag: eda

TSMC Theater Presentation: Apache

At the TSMC Theater Apache (don’t forget, now a subsidary of Ansys) talked about Emerging Challenges for Power, Signal and Reliability Verification on 3D-IC and Silicon Interposer Designs. The more I see about the costs and challenges of 20/22nm and below, the more I think that these 3D and 2.5D approaches are going to be … Read More

EDA Tools to Optimize Memory Design

I met with Amit Gupta, President and CEO of Solido at DAC on Tuesday to get an update on their EDA tools used in the design of memory, standard cells and low-power. In 2012 they’ve expanded to add three new software packages: Memory, Standard Cell, Low Power. They must be doing something right because at DAC this year I see more… Read More

Mike Muller’s ARM Keynote at DAC 2012

Mike Muller’s keynote focused on a lot of changes since the ARM1 was designed in 1983 when ARM the company did not exist and ARM was the next generation processor for Acorn Computer, which was really in the hobby market and had its first boost when they had a contract to design the BBC Microcomputer to go along with a computer literacy… Read More

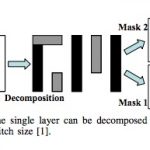

Double Patterning Technology at DAC

David Abercrombie from Mentor Graphics met with me on Tuesday at DAC to provide an update on DPT – Double Patterning Technology, something new required for several layers starting at the 20nm node in order to get any IC yield. DPT is also part of Multiple-Patterning.… Read More

IPL Alliance at DAC

Lunch on Tuesday at DAC was sponsored by the IPL Alliance and thankfully this year they skipped the attempt at humor and focused on interoperable PDKs. Presenting companies include: Synopsys, Dongbu HiTek, TowerJazz, X-FAB and Si2. Having both OpenPDK and iPDK on the same platform does sound like a peaceful co-existence to me,… Read More

Atrenta Aquires NextOp

Atrenta announced today that it is acquiring NextOp Software. NextOp sells a tool BugScope that provides assertion synthesis technology. This complements Atrenta’s SpyGlass products for improving the process for design of complex semiconductor IP and SoCs.

I went to Atrenta’s office to talk to Ajoy Bose (CEO)… Read More

Executive Opinion: The Future of EDA is Bright

The days following a major conference like DAC are a good time to reflect on the overall health and vibrancy of the electronic design automation (EDA) industry. I’ve been in EDA for 21 years and built two successful startups, and over the last couple of years, have witnessed some decline in both new talent and in venture investment… Read More

Analog Macromodels at DAC

I use social media 7 days a week and while at DAC I received a message from Herve Guegan on my LinkedIn account where he basically said, “Hey, go check out Asygn at DAC, they do analog macro models.”… Read More

What’s new with HSPICE at DAC?

One year ago I met with Hany Elhak of Synopsys to get an update on what was new with HSPICE in 2011, so this year at DAC Hany met me at the Synopsys booth for a quick update.

HSPICE has something called Precision Parallel so with 16 cores your IC circuit simulations will have about 10 x speed up compared to a single core.… Read More