You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

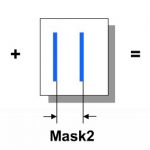

You can’t have failed to notice that 20nm is coming. There are a huge number of things that are different about 20nm from 28nm, but far and away the biggest is the need for double patterning. You probably know what this is by now, but just in case, here is a quick summary.

Lithography is done using 193nm light. Today we use immersion… Read More

I sat down last week with Paul Traynar who was over from UK. He is Apache’s PowerArtist guru. The first thing we talked about was PowerArtist’s sequential power reduction capabilities.

Forward propagation of enables means that when a register is clock gated and feeds a downstream register then that register can be… Read More

Clearly the fabless semiconductor ecosystem is driving the semiconductor industry and is responsible for both the majority of the innovation and the sharp decline in consumer electronics costs we have experienced. By definition, a fabless semiconductor company does not have to spend the time and money on manufacturing related… Read More

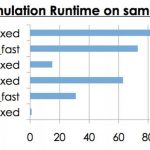

Next week December 10-12th is the Microprocessor Test and Verification (MTV 2012) which is in Austin Texas (as DAC will be next year, of course). After lunch on Monday there is a panel session on the effectiveness of virtual prototyping entitled When simulation suffices, who needs FPGA or emulation? Bill Neifert, the CTO of Carbon… Read More

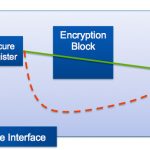

One challenge with security in systems is to ensure that there are not backdoors, either accidentally or maliciously inserted. Intel, ARM and others have various forms of trusted execution technology. Under the hood these are implemented by dividing the design into two parts, normal and secure, and implementing them with physical… Read More

Wanna become the double patterning guru at your company? David Abercrombie, DFM Program Manager for Calibre, has written a series of articles detailing the multifaceted impacts of double patterning on advanced node design and verification. For designers struggling to understand the complexity and nuances of double patterning,… Read More

One of the decisions that needs to be made when using high-level synthesis (HLS) in general and Catapult in particular is what language to use as input. The choice is C++ or SystemC. Of course at some level SystemC is C++ with added libraries and templates, but in fact the semantics of the two languages end up being very different.

The… Read More

I reviewed the book Mixed-Signal Methodology Guidein August of this year published by Cadence, and decided to follow up with one of the authors, Michael Henrie from ClioSoft, to learn more about the importance of Design Management for AMS. Michael is a Software Engineering Manager at ClioSoft and has worked at Zarlink Semi, Legerity,… Read More

It seems that Ateris vs. Sonics war, initiated by Sonics in 2010 on the legal battle field, is now continuing on the marketing field, as far as I am concerned, I prefer the latter, as I am an engineer and not a lawyer, and I must say that playing in the marketing allow both companies to extract the most attractive features of their products.… Read More

IC designers using advanced nodes are acutely aware of how variation effects in the silicon itself are causing increased analysis and design efforts in order to yield chips at acceptable levels. Four authors from Solidoare so passionate about this topic that they combined their years of experience into a book that I had a chance… Read More