I was asked to make some predictions about the EDA, semiconductor and electronic systems markets for 2013. I decided that it would be more fun to make some plausible predictions, some of which will be right, rather than go for anodyne predictions (“Cadence will acquire a couple of startups”) which are uninformative,… Read More

Tag: eda

Reducing Dynamic and Static Power in Memories

Sequential approaches to power reduction work well on logic implemented using standard cells. But part of every SoC, sometimes a very large part, is taken up with embedded memories for which alternative approaches are required. Not only do these memories occupy up to half of the area they also account for as much as 75% of the power… Read More

Global Design Closure

Satish Soman, chief solutions architect at Atrenta, was invited to give a presentation on Global Design Closure at the VLSI India conference in Pune at the start of this month. He talked about the need to close the gap between the typical SoC development methodology and what happens in reality.

SoCs are really put together in two … Read More

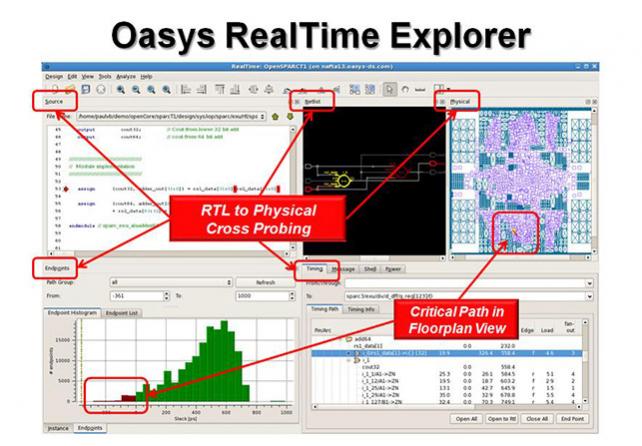

Oasys RealTime Explorer

The current methodology in design in most companies, and certainly many of the biggest, is that front end RTL design is done by one team with a limited set of front-end design tools. This is then eventually passed off to the physical design team who run all the scripts, do the “real” synthesis, place & route and timing… Read More

Are you good at identifying languages? Win an iPad Mini

Did you watch Atrenta’s holiday video (it’s only one minute)? Various Atrenta employees from all over the world wished you happy holidays in their own languages. Now Atrenta are having a competition. If you identify all the languages in the video then you can win an iPad Mini.

To enter the competition, or to view the … Read More

HiFi Mini, Always Listening

Next week it is the Consumer Electronics Show (CES) in Las Vegas and so there are announcements around the areas where consumer overlaps with semiconductor, which these days is primarily mobile. Then in February in Barcelona is Mobile World Congress, which is even more focused on mobile. Expect more announcementst there.

Currently… Read More

Happy New Year from SemiWiki!

It was an amazing year for SemiWiki and I would like to sincerely thank all who participated. SemiWiki traffic doubled again which is amazing in itself. SemiWiki membership more than tripled as we continue to add vertical markets (EDA, IP, Services, Foundry). More people are blogging on SemiWiki and the Forums and Wikis are coming… Read More

Cadence 3D Methodology

A couple of weeks ago was the 3D Architectures for Semiconductor Integration and Packagingconference in Redwood City. Cadence presented the changes that they have been making to their tool flow to enabled 2.5D (interposer-based) and true 3D TSV-based designs. You know what TSV stands for by now right? Through-silicon-via, … Read More

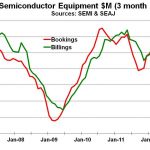

Equipment Down 16% in 2012, Flat to Down in 2013

Shipments of semiconductor manufacturing equipment have been trending downward since June 2012, based on combined data from SEMI for North American and European manufacturers and from SEAJ for Japanese manufacturers. The market bounced back strongly in late 2009 and in 2010 after the 2008 downturn to return to the $3 billion… Read More

Formal Verification at ARM

There are two primary microprocessor companies in the world these days: Intel and ARM. Of course there are many others but Intel is dominant on the PC desktop (including Macs) and ARM is dominant in mobile (including tablets).

One of the keynotes at last month’s Jasper User Group (JUG, not the greatest of acronyms) was by Bob… Read More