You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

Tom Feist of Xilinx presented here at the GlobalPress Electronics Summit about their strategy to take design abstraction up another level. In the SoC world, we are still pretty much stuck at the RTL level and have moved to higher abstractions by using an IP strategy. But at least all IC designers are RTL-literate.

Xilinx, in the Vivado… Read More

We’ve blogged before about Layout Dependent Effects (LDE) on SemiWiki and how it further complicates the IC design and layout process, especially at 28nm and lower nodes because the IC layout starts to change the MOS device performance. There’s an interesting webinarfrom Cadence on Variation-aware IC Design, … Read More

Chasing DP Rabbitsby SStalnaker on 04-15-2013 at 4:00 pmCategories: EDA, Siemens EDA

“Now, here, you see, it takes all the running you can do, to keep in the same place. If you want to get somewhere else, you must run at least twice as fast as that!”

—Lewis Carroll, Through the Looking Glass

The use of stitching can greatly reduce the number of double patterning (DP) decomposition violations that a designer has to resolve.… Read More

This was the 19[SUP]th[/SUP] annual TSMC Symposium and by far the best I have attended. Finally tired of the misinformation that plagues our industry, TSMC set the record straight with wafer and silicon correlated data. TSMC shipped more than 88 MILLION logic wafers in 2012, more than any other semiconductor company, that gives… Read More

The Electronic Design Process Symposium (EDPS) is April 18 & 19 in Monterey. The workshop style Symposium is in its 20[SUP]th[/SUP] year. The first session is titled “ESL & Platforms”, which immediately follows the opening Keynote address by Ivo Bolsens, CTO of Xilinx.

In his keynote presentation Ivo will present how… Read More

SemiWiki broke the story yesterday about the Cadence legal action against Berkeley Design Automation and today I spent time with customers of both companies in Silicon Valley getting reactions. That is the advantage of working in Silicon Valley for almost 30 years, if you don’t know the right people, you certainly know the people… Read More

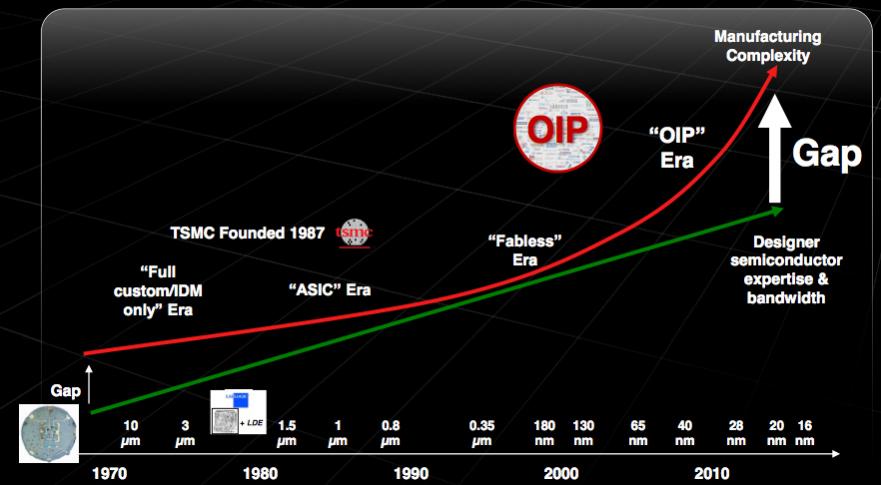

Fabless to OIPby Paul McLellan on 04-10-2013 at 7:22 pmCategories: Uncategorized

Suk Lee drew the short straw at the TSMC Symposium yesterday, with the 5pm slot. Not only late in the day but between all the attendees and free beer. The morning sessions had been standing room only, with several hundred standees (as they call them on muni around here, but isn’t a standee really someone being stood on?). But … Read More

I talked to Michael Buehler-Garcia about the changes Mentor is making to U2U, their user conference. It is in San Jose on April 25th at the DoubleTree.

Firstly, there are 3 great keynotes, two of whom I’ve seen speak before and can unreservedly recommend. Unfortunately I’m traveling that week and won’t be able… Read More

Cadence has brought a suit against Berkeley Design Automation for, as far as I can see, integrating their AFS circuit simulator with the Virtuoso Analog Design Environment (ADE) without using the (licensed) Oasis product. Since BDA is (actually was) a member of the Cadence Connections program, they have to abide by the contract… Read More

As we have moved towards lower process nodes to improve performance of ICs with higher density and functionality, many manufacturing effects have appeared which can render ICs useless, even though the layout design could be correct as per traditional design rules. What is more worrisome is the variability of these effects which… Read More