You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

My friend and fellow blogger Kurt Shuler wrote recently, “DAC Is Dead? Long Live DAC!”, which is worth a click over. In addition to providing a nice attendance graph and the top three reasons why it is NOT all rosy, Kurt suggests colocating DAC with other conferences (DESIGN West) but fails to mention SEMICON West.

SEMICON West is … Read More

Easy SystemC Debuggingby Randy Smith on 07-03-2013 at 7:00 pmCategories: EDA

Electronic system design has been slowly migrating to higher level languages such as SystemC for more than a decade now. SystemC is an open source C++ library that has emerged as a standard for high-level design and system modeling. Writing code in SystemC has several advantages which I won’t elaborate on in this article, though… Read More

If DAC is the most general event in our industry, then the LicenseMonitor Users’ Group Silicon Valley has to be one of the most focused. It was held back in May but one of the key presentations was Brian Janes of RTDA talking about what is new in the latest version of LicenseMonitor which is 2013.03.

Like a number of people at RTDA,… Read More

VLSI Technology was founded in 1981 by Dan Floyd, Jack Baletto and Gunnar Wetlesen who had worked together at Signetics. The initial investments were by Hambrecht and Quist, a cross between a VC and a bank, and by Evans and Sutherland, the simulation/graphics company.

The fourth person to join the company was Doug Fairbairn. He … Read More

During my trip to Taiwan I hopped on over to Hong Kong for a speaking engagement. One of the things I do as an “Internationally Recognized Industry Expert” is help the financial world understand the semiconductor landscape as it pertains to SoCs and mobile devices. Usually I do this over the phone or in writing but I prefer to do it in… Read More

What do nVidia, Freescale and GlobalFoundries have in common? They are semiconductor companies? They are ARM licensees? They are doing 28nm chips? They all have the letter ‘a’ in their names?

All true, but that’s not what I was thinking of. But the letter ‘a’ is a clue since Apache (and Ansys) begin with ‘a’. All three companies have… Read More

Aart de Geus gave one of the visionary look to the next 50 years of EDA as a warmup to Stephen Wu’s keynote. EDA is enabling the greatest push-pull ever, part of an exponential change on a scale never before seen.

Technologies seem to go through a 50 year technical push phase (driven by improving the technology) followed by a 50… Read More

I first met Michael Munseyback at Viewlogic in the 1990’s, so was pleased to meet with him at DACand get an update on what Dassault Systemes has to offer the EDA world.

Michael Munsey, Dassault Systemes

… Read More

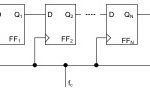

In Part 1 of this topic I discussed what it takes to estimate the mean time between failures (MTBF) of a single stage synchronizer. Because supply voltages are decreasing and transistor thresholds have been pushed up to minimize leakage, the shortened MTBF of many synchronizer circuits at nanoscale process nodes is presenting… Read More

The power of the fabless semiconductor ecosystem never ceases to amaze me. On one hand you have the Intel backed press crowing about Intel stealing Altera from TSMC. On the other hand you have Xilinx and TSMC crowing about a new ‘one-team’ approach. If you are interested in the real story you’ve come to the right place.

“Altera’s… Read More