The first article in this series examined how feasibility exploration enables architects to evaluate multi-die system configurations while minimizing early design risk. Once architectural decisions are validated, designers must translate conceptual connectivity requirements into physical interconnect infrastructure.… Read More

Tag: eco

Webinar Preview – Addressing Functional ECOs for Mixed-Signal ASICs

An engineering change order, or ECO in the context of ASIC design is a way to modify or patch a design after layout without needing to re-implement the design from its starting point. There are many reasons to use an ECO strategy. Some examples include correcting errors that are found in post-synthesis verification, optimizing … Read More

WEBINAR: Functional ECO Solution for Mixed-Signal ASIC Design

This webinar, in partnership with Easy-Logic Technology, is to address the complexities and challenges associated with functional ECO (Engineering Change Order) in ASIC design, with a particular focus on mixed-signal designs.

The webinar begins by highlighting the critical role of mixed-signal chips in modern applications,… Read More

Easy-Logic and Functional ECOs at #61DAC

I first visited Easy-Logic at DAC in 2023, so it was time to meet them again at #61DAC in San Francisco to find out what’s new this year. Steven Chen, VP Sales for North America and Asia met with me in their booth for an update briefing. Steven has been with Easy-Logic for six years now and earned an MBA from Baruch College in New York. This… Read More

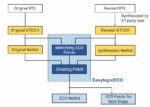

ECO Demo Update from Easy-Logic

I first met Jimmy Chen from Easy-Logic at #60DAC and wrote about their Engineering Change Order (ECO) tool in August 2023. Recently we had a Zoom call so that I could see a live demo of their EDA tool in action. Allen Guo, the AE Manager for Easy-Logic gave me an overview presentation of the company and some history to provide a bit of context.… Read More

Visit with Easy-Logic at #60DAC

I had read a little about Easy-Logic before #60DAC, so this meeting on Wednesday in Moscone West was my first in-person meeting with Jimmy Chen and Kager Tsai to learn about their EDA tools and where they fit into the overall IC design flow. A Functional Engineering Change Order (ECO) is a way to revise an IC design by updating the smallest… Read More

Sign Off Design Challenges at Cutting Edge Technologies

As semiconductor designs for many popular products move into smaller process nodes, the need for effective and rapid design closure is increasing. The SOCs used for many consumer and industrial applications are moving to FinFET nodes from 16 to 7nm and with that comes greater challenges in obtaining design closure. einfochips,… Read More

Tempus: Delivering Faster Timing Signoff with Optimal PPA

In July, I explored the benefits of the new Cadence Tempus™ Power Integrity Solution. In that piece, I explored some of the unique capabilities of this new tool with Brandon Bautz, senior product management group director and Hitendra Divecha, product management director in the Digital & Signoff Group at Cadence. I recently… Read More

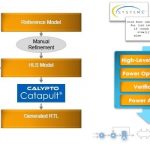

Leveraging HLS/HLV Flow for ASIC Design Productivity

Imagine how semiconductor design sizes leapt higher with automation in digital design, which started from standard hardware languages like Verilog and VHDL; analog design automation is still catching up. However, it was not without a significant effort put in moving designers from entering schematics to writing RTL, which… Read More

Synopsys Vision on Custom Automation with FinFET

In an overwhelmingly digital world, there is a constant cry about the analog design process being slow, not automated, going at its own pace in the same old fashion, and so on. And, the analog world is not happy with the way it’s getting dragged into imperfect automation so it can be more like the digital world. True, the analog world… Read More