The relentless demand for lower power SoCs is evident across many markets. Examples include cutting-edge mobile, IoT, and wearable devices along with the high compute demands for AI and 5G/6G communications. Drivers for low power include battery life, thermal management and, for high compute applications, the overall cost… Read More

Tag: dvfs

Staying on the Right Side in Worst Case Conditions – Performance (Part 2)

In this, the second part of a two-part series we delve further into defining worst case, this time focusing specifically on device performance.

In the last blog we talked about the steady increase in power density per unit silicon area and how worst case is definitely getting worse. We discussed how in each new FinFET node the dynamic… Read More

How to Increase Energy Efficiency for IoT SoC?

If you have read the white paper recently launched by Dolphin, “New Power Management IP Solution from Dolphin Integration can dramatically increase SoC Energy Efficiency”, you should already know about the theory. This is a good basis to go further and discover some real-life examples, like Bluetooth Low Energy (BLE) chip in … Read More

Integrated Power Management IP to Decrease Power and Cost

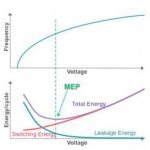

This blog is the synthesis of a white paper “New Power Management IP Solution from Dolphin Integration can dramatically increase SoC Energy Efficiency”, which can be found on Dolphin Integration web site.

The power consumption generated by complex chips was not a real issue when the system could be simply plugged in the wall to … Read More

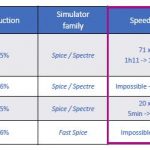

It’s Time to Put Your Spice Netlists on a Diet

Spice circuit simulation remains the backbone of IC design validation. Digital cell library developers rely upon Spice for circuit characterization, to provide the data for Liberty models. Memory IP designers utilize additional Spice features to perform statistical sampling. Analog and I/O interface designers extend these… Read More

SoC power management a study in transition latency

Apple’s recent bout with ‘Batterygate’ highlighted just how important dynamic power management can be. Our last Sonics update looked at using their NoC to manage power islands; this time, we look at their research progress on architectural measures for power management.… Read More

Networking through Dark Silicon Power Islands

For decades, tracing back to the days of Deming, the way to tackle complex engineering problems has been the pareto chart. Charting conditions and their contribution to the problem leads to mitigation priorities.

In the case of SoC power management, the old school pareto chart said the processor core was the biggest power hog and… Read More

NoCs for system-level power management

Most of the buzz on network-on-chip is around simplifying and scaling interconnect, especially in multicore SoCs where AMBA buses and crossbars run into issues as more and more cores enter a design. Designers may want to explore how NoCs can help with a more power-aware approach.… Read More

The Secret Essence of an IoT Design

Today the semiconductor industry along with electronics industry is looking up to capitalize from massive expansion foreseen in IoT (Internet of Things) domain. In simple terms we can consider IoT as connectivity between machines which can communicate with each other and work as programmed. In localized applications such … Read More

Non-separation of power and performance

How much power does a system consume? The simplistic path to power estimation for a system used to be tossing a few metrics – standby, typical, worst case, with figures pulled from a datasheet, simulation, or physical measurement – into a spreadsheet. After filling the remaining holes with SWAG (scientific wild-ass guesses), … Read More