It seems like I have written a lot about SRAM lately. Let’s face it SRAM is important – it often represents large percentages of the area on SOC’s. As such, SRAM yield plays a major role in determining overall chip yields. SRAM is vulnerable to defect related failures, which unlike variation effects are not Gaussian in nature. Fabrication… Read More

Tag: defect

No EUV before 7nm?

I was at the Common Platform Technology Forum this week. One of the most interesting sessions is IBM’s Gary Patton giving an overview of the state of semiconductor fabrication. Then, at lunchtime, he is one of the people that the press can question. In this post, I’m going to focus on Extreme Ultra-Violet (EUV) lithography.… Read More

EUV: No Pellicle

There’s a dirty secret problem about EUV that people don’t seem to to be talking about. There’s no pellicle on a EUV mask. OK, probably you have no idea what that means, a lot of jargon words, nor why it would be important, but it seems to me it could be the killer problem for EUV.

In refractive masks, you print a pattern… Read More

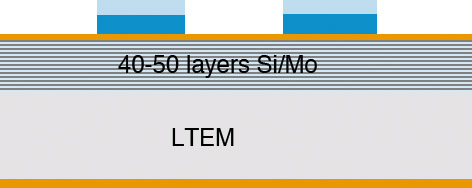

EUV Masks

This is really the second part to this blog about the challenges of EUV lithography. The next speaker was Franklin Kalk who is CTO of Toppan Photomasks. He too emphasized that we can make almost arbitrarily small features but more and more masks are required (not, that I suspect, he would complain being in the mask business). For EUV… Read More