Advanced Micro Devices has already told us that 2016 was going to be the year of graphics, but the reality is that they also have a lot going on in their CPU and APU division as well. In fact, in addition to Advanced Micro Devices’s newly announced 7th Generation APUs in 2016, the company is also expected to launch their new Zen CPU cores… Read More

Tag: ddr4

Are Standard Cell Libs, Memories and Mixed-signal IP Availabe at 7nm FF?

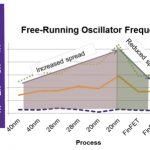

More than 500 designers (562) have responded to a survey made in 2015 by Synopsys. Answering to the question “What is the fastest clock speed of your design?” 56% have mentioned a clock higher than 500 MHz (and still 40% higher than 1 GHz). If you compare with the results obtained 10 years ago, the largest proportion of answers was for… Read More

DDR4 is a complex interface to verify — assistance needed!

The design of parallel interfaces is supposed to be (comparatively) easy — e.g., follow a few printed circuit board routing guidelines; pay attention to data/clock/strobe signal lengths and shielding; ensure good current return paths (avoid discontinuities); match the terminating resistances to the PCB trace impedance;… Read More

Interface IP year 2015: Winners and Losers

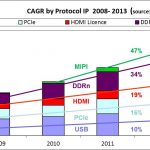

The global Interface IP market is still growing in 2015, no doubt about it. It’s interesting to zoom in the various protocols to check their respective behavior. Which protocol generates an IP business growing more than the average market? Which protocol generates a disappointing IP business? In other words, which are the winners… Read More

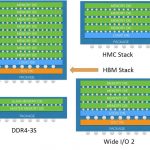

Which High B/W Memory to Select after DDR4?

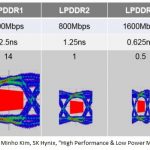

Once upon a time, RAM technology was the driver of the semiconductor process. DRAM products were the first to be designed on a newest technology node and DRAM was used as a process driver. It was 30 years ago and the most aggressive process nodes were ranging between 1um and 1.5 um (1 500 nm!). Then in the 1990 the Synchronous Dynamic … Read More

Synopsy Eats Their Own Dogfood

One of the most interesting presentations that I went to was the last presentation at the Synopsys Custom Lunch (no, the lunch wasn’t custom, we all got the same, but the presentations were about custom design). Since the last presentation was by Synopsys themselves and not by a customer, it wouldn’t seem promising that it could … Read More

Sonics’ New NoC

Today Sonics announced the latest version of their network-on-chip (NoC) technology, SonicsGN-3.0. As with any new release there are lots of improvements that are of interest mainly to existing users, but the big area with increased capability is the expanded interleaved memory technology (IMT). This was first introduced … Read More

IP-SoC 2014 Top Class Presentations…

… were given to an ever shrinking audience. This is IP-SoC paradox: audience has enjoyed very good presentations made by Cadence, Synopsys or ST-Microelectronic, to name just a few. As far as I am concerned, I was happy to present the “Interface IP Winners and Losers (Protocols)” in the amphitheater during the first day, enjoying… Read More

Interface IP Protocols: Status

If your company develops Design IP to support well-known protocols like USB, PCIe, HDMI, DDRn memory controller, MIPI specification (and more), it’s crucial to know your competition, the market size by segment, and even more important the market potential by segment. The latest can be obtained by the Compound Annual Growth Rate… Read More

Cadence white paper helps you selecting what come after DDR4

The DRAM market is shaking… In 2014, analysts predict that LPDDR4 will surpass DDR4 for the first time. When releasing DDR4 standard, JEDEC has clearly stated that the industry should not expect any DDR5. Does this means that DRAM technology new development is ending with DDR4? According with Mike Howard, principal analyst at … Read More