In a significant milestone for the semiconductor industry, Teradyne was honored as the 2025 TSMC Open Innovation Platform® Partner of the Year for TSMC 3DFabric® Testing. This award, announced on September 25, 2025, underscores the deep collaboration between Teradyne, a leader in automated test equipment and robotics, and… Read More

Tag: cowos

Alchip’s 3DIC Test Chip: A Leap Forward for AI and HPC Innovation

Today Alchip Technologies, a Taipei-based leader in high-performance and AI computing ASICs, announced a significant milestone with the successful tape-out of its 3D IC test chip. This achievement not only validates Alchip’s advanced 3D IC ecosystem but also positions the company as a frontrunner in the rapidly evolving field… Read More

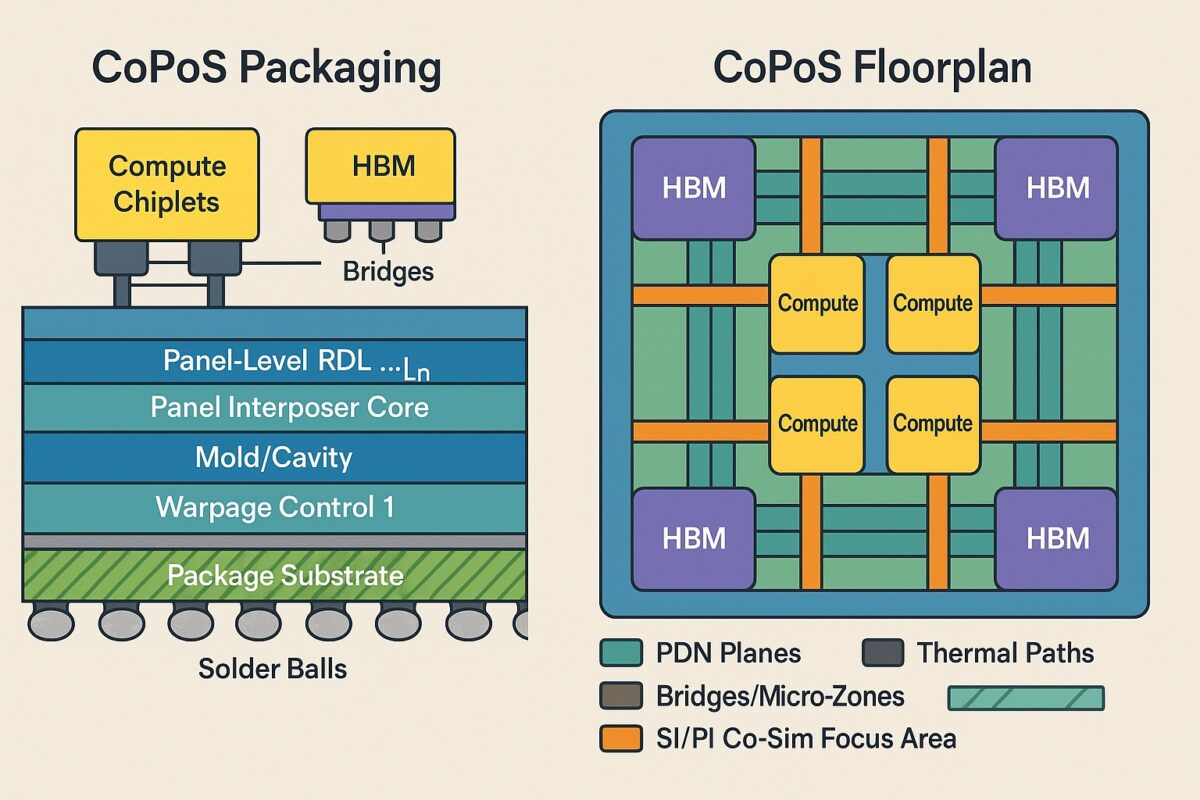

CoPoS is a Bigger Canvas for Chiplets and HBM

Alchip’s Technology and Global Talent Strategy Deliver Record Growth

Alchip Technologies Ltd., a global leader in high-performance computing (HPC) and artificial intelligence (AI) ASIC design and production services, continues its trajectory of rapid growth and technical leadership by pushing the boundaries of advanced-node silicon, expanding its global design capabilities, and building… Read More

IEDM Opens with a Big Picture Keynote from TSMC’s Yuh-Jier Mii

The main program for the 70th IEDM opened on Monday morning in San Francisco with an excellent keynote from Dr. Yuh-Jier Mii, Executive Vice President and Co-Chief Operating Officer at TSMC. Dr. Mii joined TSMC in 1994. Since then, he has contributed to the development and manufacturing of advanced CMOS technologies in both fab

Alchip is Paving the Way to Future 3D Design Innovation

At the recent TSMC OIP Ecosystem Forum in Santa Clara, there was an important presentation that laid the groundwork for a great deal of future innovation. Alchip and its IP and EDA partner Synopsys presented Efficient 3D Chiplet Stacking Using TSMC SoIC. The concept of 3D, chiplet-based design certainly isn’t new. SemiWiki maintains… Read More

Alchip Technologies Sets Another Record

The ASIC business has always been a key enabler of the semiconductor industry but it is a difficult business. In my 40 years I have seen many ASIC companies come and go but I have never seen one like Alchip.

Alchip Technologies Ltd. was founded more than 20 years ago, about half way through my career. I know one of the founders, a fiercely… Read More

Maximizing 3DIC Design Productivity with 3DBlox: A Look at TSMC’s Progress and Innovations in 2024

At the 2024 TSMC OIP Ecosystem Forum, one of the technical talks by TSMC focused on maximizing 3DIC design productivity and rightfully so. With rapid advancements in semiconductor technology, 3DICs have become the next frontier in improving chip performance, energy efficiency, and density. TSMC’s focus on streamlining the… Read More

Elevating AI with Cutting-Edge HBM4 Technology

Artificial intelligence (AI) and machine learning (ML) are evolving at an extraordinary pace, powering advancements across industries. As models grow larger and more sophisticated, they require vast amounts of data to be processed in real-time. This demand puts pressure on the underlying hardware infrastructure, particularly… Read More

TSMC’s Business Update and Launch of a New Strategy

What looks like a modest market expansion strategy is all but modest.

Insights into the Semiconductor Industry and the Semiconductor Supply Chain.

As usual, when TSMC reports, the Semiconductor industry gets a spray of insights that help understand what goes on in other areas of the industry. This time, TSMC gave more insight … Read More