You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

In the 3D-IC (Three-dimensional integrated circuit) chip design method, chiplets or wafers are stacked vertically on top of each other and are connected using Through Silicon Vias (TSVs) or hybrid bonding.

The 2.5D-IC design method places multiple chiplets alongside each other on a silicon interposer. Microbumps and interconnect… Read More

For decades now I’ve watched the incredible growth of SoCs in terms of die size, transistor count, frequency and complexity. Instead of placing all of the system complexity into a single, monolithic chip, there are now compelling reasons to use a multi-chip approach, like when the maximum die size limit is reached, or it’s… Read More

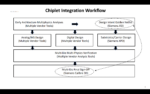

Chiplet-based System-on-Chips (SoCs) are becoming increasingly popular in the semiconductor industry due to their potential to improve design efficiency, increase performance, and reduce costs. While chiplets are seen as a way to reduce the cost of innovation, they introduce a lot of challenges too. Packaging, interconnect… Read More

At the recent Synopsys Users Group Meeting (SNUG) I had the honor of leading a panel of experts on the topic of chiplets. One of those panelists was John Lee, Head of Electronics, Semiconductors and Optics at Ansys.

How is the signoff flow evolving and what is being done to help mitigate the growing signoff complexity challenge?

With… Read More

Chiplet is a hot topic in the semiconductor world these days. So much so that if one hasn’t heard that term, the person must be living on a very isolated islet. Humor aside, products built using chiplets-based methodology have been in existence for at least some years now. Companies such as Intel, AMD, Apple and others have integrated… Read More

Every country realizes the importance of producing skilled chip designers who could decide their success as soldiers by creating advanced AI chips for winning the Chip War. Also, every country is now gearing up to build a good semiconductor manufacturing ecosystem to balance the global semiconductor supply chain that could … Read More

At the recent Synopsys Users Group Meeting (SNUG) I had the honor of leading a panel of experts on the topic of chiplets. One of those panelists was the very personable Dr. Henry Sheng, Group Director of R&D in the EDA Group at Synopsys. Henry currently leads engineering for 3DIC, advanced technology and visualization.

Are we

…

Read More

At the recent Synopsys Users Group Meeting (SNUG) I had the honor of leading a panel of experts on the topic of chiplets. The discussion was based on a report published by the MIT Technology Review Insights in cooperation with Synopsys. This is a very comprehensive report (12 pages) that is available online HERE.

Here is the preface… Read More

Multiphysics simulation is the process of computational methods to model and analyze a system to understand its response to different physical interactions like heat transfer, electromagnetic fields, and mechanical structures. Using this technique, designers can generate physics-based models and analyze the behavior… Read More

Chiplets appeared on SemiWiki in 2020 and have been a top trending keyword ever since. The question is not IF chiplets will disrupt the semiconductor industry, the question is WHEN? I certainly have voiced my opinion on this (pro chiplet) but let’s hear it from the experts. There was a live panel recently sponsored by Silicon Catalyst… Read More