Anna has more than 25 years of expertise in managing complex R&D organizations and programs, giving birth to a number of innovative EDA technologies. She has pioneered the study and development of several generations of IC and package co-design environments and has held senior positions at leading semiconductor and EDA … Read More

Tag: chiplet

Alphawave Semi Visit at #60DAC

On Wednesday at #60DAC I met Sudhir Mallya, Sr. VP Corporate Marketing at Alphawave Semi to get an update about what’s been happening at their IP company and with industry trends. The tagline for their company is: Accelerating the Connected World; and they have IP for connectivity, offer chiplet solutions, and even provide… Read More

Requirements for Multi-Die System Success

Chiplets continue to be a hot topic on SemiWiki, conferences, white papers, webinars and one of the most active chiplet enabling vendors we work with is Synopsys. Synopsys is the #1 EDA and #1 IP company so that makes complete sense.

As you may have read, I moderated a panel on Chiplets at the last SNUG which we continue to write about.

TSMC Doubles Down on Semiconductor Packaging!

Last week TSMC announced the opening of an advanced backend fab for the expansion of the TSMC 3DFabric System Integration Technology. It’s a significant announcement as the chip packaging arms race with Intel and Samsung is heating up.

Fab 6 is TSMC’s first all-in-one advanced packaging and testing fab which is part of the… Read More

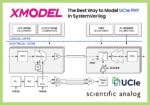

WEBINAR: UCIe PHY Modeling and Simulation with XMODEL

Join this webinar and see UCIe in action! This webinar presents the SystemVerilog models of a Universal Chiplet Interconnect Express (UCIe) interface, including both the analog circuits in the electrical layer and digital FSMs in the logical layer. The whole physical layer (PHY) model can be efficiently simulated in SystemVerilog,… Read More

eFPGA Enabled Chiplets!

With our continuing chiplet coverage I found this of great interest. I have always felt that eFPGAs and chiplets are a natural fit for the next generation of chip design and this is an excellent example. As we design with chiplets one of the challenges is verification/validation in regards to performance and interoperability. … Read More

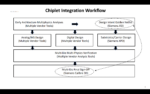

Chiplet Modeling and Workflow Standardization Through CDX

Chiplet is a hot topic in the semiconductor world these days. So much so that if one hasn’t heard that term, the person must be living on a very isolated islet. Humor aside, products built using chiplets-based methodology have been in existence for at least some years now. Companies such as Intel, AMD, Apple and others have integrated… Read More

The Rise of the Chiplet

The emergence of chiplets as a technology is an inflection point in the semiconductor industry. The potential benefits of adopting a chiplets-based approach to implementing electronic systems are not a debate. Chiplets, which are smaller, pre-manufactured components can be combined to create larger systems, offering benefits… Read More

Checklist to Ensure Silicon Interposers Don’t Kill Your Design

Traditional methods of chip design and packaging are running out of steam to fulfill growing demands for lower power, faster data rates, and higher integration density. Designers across many industries – like 5G, AI/ML, autonomous vehicles, and high-performance computing – are striving to adopt 3D semiconductor… Read More

Speeding up Chiplet-Based Design Through Hardware Emulation

The first chiplets focused summit took place last month. So many accomplished speakers gave keynote talks on what direction should and would the Chiplets ecosystem evolution take. Corigine presented the keynote on what direction hardware emulation should and would evolve for speeding up chiplet- based designs. During a pre-conference… Read More