Steve Kommrusch of AMD wrote a white paper with Calypto on how AMD reduced power by 20% on the Jaguar SoC using Calypto’s PowerPro. Dan Nenni blogged about it on SemiWiki back in February here. And now, drumroll, Steve will present the story live and in person at DAC, on Monday June 3rd at 3pm and on Wednesday June 5th at 11am. This… Read More

Tag: calypto

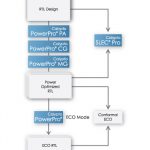

Calypto, in Three Part Harmony

As Julius Caesar said, “Gallia est omnis divisa in partes tres.” All Gaul is divided into 3 parts. Calypto is similar with three product lines that work together to provide a system level approach to SoC design. Two of those product lines are not unique, in the sense that similar capabilities are available from a handful… Read More

DAC: Calypto Insight Presentation

DAC has several “Insight Presentations” on Wednesday June 5th. Bryan Bowyer from Calypto will be presenting from 2-4pm that day (don’t know where, the DAC website doesn’t have a room number specified yet). The topic is Reducing Design and Debug Time with Synthesizable TLM. TLM, of course, stands for… Read More

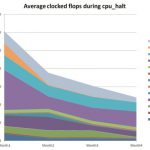

Clock Gating: Sequential Is Better

Sequential clock gating offers more power savings that can be obtained just with combinational clock gating. However, sequential clock gating is very complex as it involves temporal analysis over multiple clock cycles and examination of the stability, propagation, and observability of signal values.

Trying to do sequential… Read More

Sanjiv Kaul: Is HLS About to Take Off?

At the end of last week I talked to Sanjiv Kaul, the new CEO of Calypto. Just to give a little background for those that haven’t been following along at home, Calypto was founded to try and solve the very hard problem of sequential logical equivalence checking (mostly by people from the engineering team that I managed at Ambit).… Read More

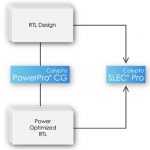

High and Low: High Level Synthesis and Low Power

It is so widely accepted that it is already a cliche to say that “power is the new timing.” With more and more chips, the major challenge is not so much to meet timing but to meet timing without blowing out the power budget. Otherwise, you could just crank up the clock rate.

I’m going to be lazy so you can insert your … Read More

RTL Clock Gating Analysis Cuts Power by 20% in AMD Chip!

Approximately 25% of SemiWiki traffic originates from search engines and the key search terms are telling. Since the beginning of SemiWiki, “low power design” has been one of the top searches. This is understandable since the mobile market has been leading us down the path to fame and fortune. Clearly lowering the… Read More

Sanjiv Kaul is New CEO of Calypto

Calypto announced that Sanjiv Kaul is the new CEO. I first met Sanjiv many years ago when he was still at Synopsys when I interviewed for a position there around the time I transitioned out of Compass and went back to the parent company VLSI. I forget what the position was. Then about three or four years ago when I did some work for Oasys… Read More

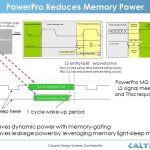

Dynamic/Leakage Power Reduction in Memories

Embedded memories have an important impact on power. SoCs that integrate multiple functions on a single silicon die are at the heart of many electronic devices. As process geometries have scaled, design teams have used more and more of the additional silicon real estate available to integrate embedded memories that serve as scratch-pads,… Read More

Reducing Dynamic and Static Power in Memories

Sequential approaches to power reduction work well on logic implemented using standard cells. But part of every SoC, sometimes a very large part, is taken up with embedded memories for which alternative approaches are required. Not only do these memories occupy up to half of the area they also account for as much as 75% of the power… Read More