As semiconductors become more integrated into our lives reliability is becoming a critical issue. As IP consumes more of our die, IP reliability is becoming a critical issue. As we pack more transistors into a chip, reliability is becoming a critical issue. As we move from 28nm to 20nm to 16nm, reliability is becoming a critical … Read More

Tag: calibre perc

How to Simplify Complexities in Power Verification?

With multiple functionalities added into a single chip, be it a SoC or an ASIC, maintaining low power consumption has become critical for any design. Various techniques at the technology as well as design level are employed to accomplish the low power target. These include thinner oxides in transistors, different sections of … Read More

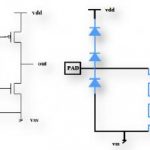

A Programmable Electrical Rule Checker

IC designers involved with physical design are familiar with acronyms like DRC (Design Rule Check), LVS (Layout Versus Schematic) and DFM (Design For Manufacturing), but how would you go about checking for compliance with ESD (Electro Static Discharge) rules? You may be able to kludge something together with your DRC tool and… Read More

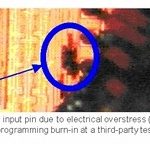

ESD – Key issue for IC reliability, how to prevent?

It’s a common electrical rule that when large amount of charge gets accumulated, it tries to break any of its surrounding isolation. Although it wouldn’t have been prominent in 1980s or 90s, protection for ICs from such damaging effects is a must, specifically in large mixed-signal designs of today, working at different voltages… Read More

IC Reliability and Prevention During Design with EDA Tools

IC device physics uncovers limits to reliable operation, so IC designers are learning to first identify and then fix reliability issues prior to tape-out. Here’ s a list of reliability issues to keep you awake at night:… Read More

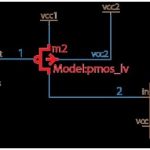

Transistor-Level Electrical Rule Checking

Introduction

Circuit designers work at the transistor level and strive to get the ultimate in performance, layout density or low power by creating crafty circuit topologies in both schematics and layout. Along with this quest comes the daunting task of verifying that all of your rules and best practices about reliability have… Read More

Intel Sandy Bridge Fiasco and EDA

I purchased two Toyotas last year and both have since been recalled. Why has Toyota spent $1B+ on recalls in recent years? Same reason why it will cost Intel $700M (which does not include reputation damage) to recall Sandy Bridge chip sets, because someone did not do their job! The WHAT has been discussed, lets talk about HOW it happened.… Read More