At #61DAC, I love it when an exhibitor booth uses a descriptive tagline to explain what they do, like when the Blue Cheetah booth displayed Advancing Chiplet Interconnectivity. Immediately, I knew that they were an IP provider focusing on chiplets. I learned what sets them apart is how customizable their IP is to support specific… Read More

Tag: BoW

Siemens Provides a Complete 3D IC Solution with Innovator3D IC

Heterogeneous multi-die integration is gaining more momentum all the time. The limited roadmap offered by Moore’s Law monolithic, single-die integration has opened the door to a new era of more-than-Moore heterogeneous integration. The prospects offered by this new design paradigm are exciting and the entire ecosystem is… Read More

Chiplet ecosystems enable multi-vendor designs

Chiplets dominate semiconductor industry conversations right now – and after the recent Chiplet Summit, we expect the intensity to go up a couple of notches. One company name often heard is Blue Cheetah, and we had the opportunity to sit down with them recently to discuss their views and their just-announced design win at Tenstorrent.… Read More

The Rise of the Chiplet

The emergence of chiplets as a technology is an inflection point in the semiconductor industry. The potential benefits of adopting a chiplets-based approach to implementing electronic systems are not a debate. Chiplets, which are smaller, pre-manufactured components can be combined to create larger systems, offering benefits… Read More

Die-to-Die Interconnects using Bunch of Wires (BoW)

Chiplets are a popular and trending topic in the semiconductor trade press, and I read about SoC disaggregation at shows like ISSCC, Hot Chips, DAC and others. Once an SoC is disaggregated, the next challenge is deciding on the die-to-die interconnect approach. The Open Compute Project (OCP) started 10 years ago as a way to share… Read More

OpenFive Joins Universal Chiplet Interconnect Express (UCIe) Consortium

Universal Chiplet Interconnect Express (UCIe) is an open specification that defines the interconnect between chiplets within a package. The objective is to enable an open chiplet ecosystem. Although the initial specification for UCIe was developed by Intel, a consortium was announced in March with Intel, AMD, Arm, Google,… Read More

Die-to-Die IP enabling the path to the future of Chiplets Ecosystem

The topic of chiplets is getting a lot of attention these days. The chiplet movement has picked up more momentum since Moore’s law started slowing down as process technology approached 5nm. With the development cost of a monolithic SoC crossing the $500M and wafer yields of large die-based chips dropping steeply, the decision … Read More

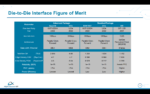

Die-to-Die Interface PHY and Controller Subsystem for Next Generation Chiplets

In early April, Gabriele Saucier kicked off Design & Reuse’s IPSoC Silicon Valley 2021 Conference. IPSoC conference as the name suggests is dedicated to semiconductor intellectual property (IP) and IP-based electronic systems. There were a number of excellent presentations at the conference. The presentations had been… Read More

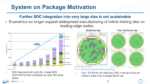

Enabling Next Generation Silicon In Package Products

In early April, Gabriele Saucier kicked off Design & Reuse’s IPSoC Silicon Valley 2021 Conference. IPSoC conference as the name suggests is dedicated to semiconductor intellectual property (IP) and IP-based electronic systems. There were a number of excellent presentations at the conference. The presentations had been… Read More