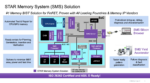

Memory testing in the early days of computing was a relatively straightforward process. Designers relied on simple, deterministic approaches to verify the functionality of memory modules. However, as memory density increased and systems became more complex, the likelihood of faults also rose. With advancements in memory… Read More

Tag: bist

Chiplets-Based Systems: Keysight’s Role in Design, Testing, and Data Management

Keysight, with deep roots tracing back to Hewlett-Packard, has long been at the forefront of innovation in electronic design and testing. It manufactures electronics test and measurement equipment and software. The company also owns its own foundry and makes custom chips and packages for its instrumentation business. Many… Read More

proteanTecs Technology Helps GUC Characterize Its GLink™ High-Speed Interface

An earlier post on SemiWiki discussed how deep data analytics helps accelerate SoC product development. The post presented insights into proteanTecs’ technology and quantified the benefits that can be derived by leveraging the software platform for SoC product development. You can review that earlier blog here. The power … Read More

Smarter Product Lifecycle Management for Semiconductors

Product Lifecycle Management (PLM) for electronic systems has moved from a passive ‘fire and forget’ approach to one that is intimately involved not only during design, but also throughout the entire life of every unit delivered to the field. Siemens EDA has a white paper titled “Tessent Silicon Lifecycle Solutions” that talks… Read More

DFT Innovations Come from Customer Partnerships

There is an adage that says that quality is not something that can be slapped on at the end of the design or manufacturing process. Ensuring quality requires careful thought throughout development and production. Arguably this adage is more applicable to the topic of Design for Test (DFT) than almost any other area of IC development… Read More

Synopsys – Turbocharging the TCAM Portfolio with eSilicon

About 90 days ago, Synopsys completed the acquisition of certain IP assets from eSilicon. The remaining entirety of eSilicon was acquired by Inphi Corporation. I was the VP of marketing at eSilicon during that acquisition so it’s very interesting to me to find out how things are going with those certain IP assets. I got an opportunity… Read More

Automotive Market Pushing Test Tool Capabilities

It’s easy to imagine that the main impetus for automotive electronics safety standards like ISO 26262 is the emergence of autonomous driving technology. However, even cars that do not offer this capability rely heavily on electronics for many critical systems. These include engine control, braking, crash sensors, and stability… Read More

In-System Automotive Test

I’ve been driving cars since 1975 and in the early days we had simplistic gauges for feedback like: Speed, Fuel level, Oil level, RPM. Back then when you popped the hood of a car you could see through the engine compartment onto the ground below, however with today’s cars the engine compartments are crammed with tubes,… Read More

Reducing the Cost of SoC Testing

Every year certain technology themes appear, like at ITC this year a big theme was how to reduce the cost of SoC testing. I spoke with Rob Knoth of Cadence by phone to hear more about this cost of test theme. Rob gave me an example of an SoC that takes 27 seconds on a tester, so at $0.04 per second in test costs amounts to $1.08 per part. If you… Read More

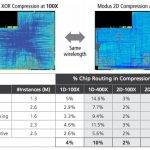

Cadence Adds New Dimension to SoC Test Solution

It requires lateral thinking in bringing new innovation into conventional solutions to age-old hard problems. While the core logic design has evolved adding multiple functionalities onto a chip, now called SoC, the structural composition of DFT (Design for Testability) has remained more or less same based on XOR-based compression… Read More