I have observed before that the success of an AI engine at the edge rests heavily on the software interface to drive that technology. Networks trained in the cloud need considerable massaging to optimize for smaller and more specialized edge devices. Moreover, an AI task at the edge depends on a standalone pipeline demanding a mix… Read More

Tag: bernard murphy

Opinions on Generative AI at CadenceLIVE

According to some AI dreamers, we’re almost there. We’ll no longer need hardware or software design experts—just someone to input basic requirements from which fully realized system technologies will drop out the other end. Expert opinions in the industry are enthusiastic but less hyperbolic. Bob O’Donnell, president, founder… Read More

Takeaways from CadenceLIVE 2023

Given popular fascination it seems impossible these days to talk about anything other than AI. At CadenceLIVE, it was refreshing to be reminded that the foundational methods on which designs of any type remain and will always be dominated in all aspects of engineering by deep, precise, and scalable math, physics, computer science… Read More

Is Your Interconnect Strategy Scalable?

“Strategy” is a word sometimes used loosely to lend an aura of visionary thinking, but in this context, it has a very concrete meaning. Without a strategy, you may be stuck with decisions you made on a first-generation design when implementing follow-on designs. Or face major rework to correct for issues you hadn’t foreseen. Making… Read More

Anirudh Keynote at Cadence Live

Anirudh is an engaging speaker with a passion for technology. Acknowledging the sign of the times, he sees significant value-add in AI but reminded us that it is a still supporting actor in system design and other applications where star roles will continue to be played by computational software that’s founded in hard science, … Read More

Petri Nets Validating DRAM Protocols. Innovation in Verification

A Petri nets blog scored highest in engagement last year. This month we review application of the technique to validating an expanding range of JEDEC memory standards. Paul Cunningham (Senior VP/GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and now Silvaco CTO) and I continue… Read More

More Software-Based Testing, Less Errata

In verification there is an ever-popular question, “When can we stop verifying?” The intent behind the question is “when will we have found all the important bugs?” but the reality is that you stop verifying when you run out of time. Any unresolved bugs appear in errata lists delivered with the product (some running to 100 or more … Read More

Siemens EDA on Managing Verification Complexity

Harry Foster is Chief Scientist in Verification at Siemens EDA and has held roles in the DAC Executive Committee over multiple years. He gave a lunchtime talk at DVCon on the verification complexity topic. He is an accomplished speaker and always has a lot of interesting data to share, especially his takeaways from the Wilson Research… Read More

Takeaways from SNUG 2023

Synopsys pulled out all the stops for this event. I attended the first full day, tightly scripted from Aart’s keynote kick off to 1×1 interviews with Synopsys executives to a fireside chat between Sassine Ghazi (President and COO) and Rob Aitken (ex-Fellow at Arm, now Distinguished Architect at Synopsys). That’s a lot of … Read More

Interconnect Under the Spotlight as Core Counts Accelerate

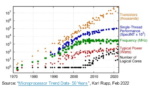

In the march to more capable, faster, smaller, and lower power systems, Moore’s Law gave software a free ride for over 30 years or so purely on semiconductor process evolution. Compute hardware delivered improved performance/area/power metrics every year, allowing software to expand in complexity and deliver more capability… Read More