Last month in DAC I could see some of the top innovations in the EDA world. EDA is a key enabler for advances in semiconductor designs. Among a number of innovations worth mentioning (about which I blogged just after DAC), the integration of Mentor’s Veloce with ANSYS’ PowerArtist for power analysis of live applications caught my… Read More

Tag: ansys

Benefits of RTL Power Budgeting

Only one company at the recent DAC conference and exhibit had a set of four interacting disciplines: Fluids, Structures, Electronics and Systems. Did you guess that the company was ANSYS? I get so IC focused at times that I almost forget that chips plug into boards, that boards become systems, and that systems drive and control mechanical… Read More

Trends in Automotive Electronics at #52DAC

The coolest and most expensive car at DAC this year had to be the McLaren P1, priced at $1,150,00 and powered by a 903 hp gas/electric hybrid. Electronics are used in autos to provide safety features, infotainment, motor control and performance.

Also at DAC this year there was an Automotive Village with more cars and experts from … Read More

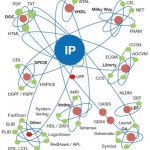

An Universe of Formats for IP Validation

Although I knew about Crossfire’s capabilities for signing off quality of an IP before its integration into an SoC, there was much more to learn about this tool when I visited Fractal Technologies booth during this DAC. The complexity handled by this tool to qualify any type of IP for its integration into an SoC can be imagined by the… Read More

Eyes Meet Innovations at DAC

It gives me a very nice, somewhat nostalgic, feeling after attending the 52[SUP]nd[/SUP] DAC. There was a period during my final academic year in 1990 and my first job when I used to search through good technical papers in DAC proceedings and try implementing those concepts in my project work. In general, representation from ‘R&D… Read More

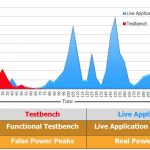

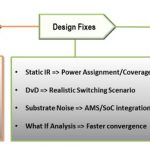

Getting the Best Dynamic Power Analysis Numbers

On your last SoC project how well did your dynamic power estimates match up with silicon results, especially while running real applications on your electronic product? If your answer was, “Well, not too good”, then keep reading this blog. A classical approach to dynamic power analysis is to run your functional testbench… Read More

A Key Partner in the Semiconductor Ecosystem

Often we hear about isolated instances of excellence from various companies in the semiconductor industry which contribute significantly in building the overall ecosystem. While the individual excellence is essential, it’s rather more important how that excellence is utilized in a larger way by the industry to create a ‘value… Read More

Fractal at DAC 2015 – What’s new?

I have been observing Fractal Technologiesexhibiting at DACyear after year, and every year they have demonstrated good value added features in their tools for SoC and IP development. This year at 52[SUP]nd[/SUP] DAC Fractal’s booth number is 1110. Earlier in this year Fractal had added a new ‘Cdiff’ feature in its flagship product… Read More

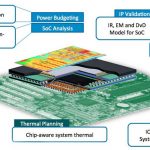

Will your next SoC fail because of power noise integrity in IP blocks?

By the time that your SoC comes back from the fab and you plugin it into a socket on a board for testing, it’s a little late in the cycle to start thinking about reliability concerns like: dynamic voltage drop, noise coupling, EM (Electro-Migration), self-heating, thermal analysis and ESD (Electro-Static Discharge). They… Read More

ANSYS Enters the League of 10nm Designs with TSMC

The way we are seeing technology progression these days is unprecedented. It’s just about six months ago, I had written about the intense collaboration between ANSYSand TSMCon the 16nm FinFET based design flow and TSMC certifying ANSYS tools for TSMC 16nm FF+ technology and also conferring ANSYS with “Partner of the Year” award.… Read More