System on chip (SoC) based design has long been recognized as a powerful method to offer product differentiation through higher performance and expanded functionality. Yet, it comes with a number of limitations, such as high cost of development. Also, SoCs are monolithic, which can inhibit rapid adaptation in the face of changing… Read More

Tag: 3d-ic

Ansys Multiphysics Platform

Background

Traditionally, the interface between chip designers and system power, packaging, reliability, and mechanical engineering teams was a relatively straightforward exchange of specifications. Chip designers developed preliminary power dissipation estimates, often based on a simplifying power/mm**2 value. … Read More

Driving PPA Optimization Across the Cubic Space of 3D IC Silicon Stacks

The move to true 3D IC, monolithic 3D SOC and 3D heterogeneous integration may require one of the most major design tool architecture overhauls since IC design tools were first developed. While we have been taking steps toward 3DIC with 2.5D designs with interposers, HBM, etc., the fundamental tools and flows remain intact in many… Read More

CEO Interview: Anna Fontanelli of Monozukuri

Anna has more than 25 years of expertise in managing complex R&D organizations and programs, giving birth to a number of innovative EDA technologies. She has pioneered the study and development of several generations of IC and package co-design environments and has held senior positions at leading semiconductor and EDA … Read More

TSMC’s Advanced IC Packaging Solutions

TSMC as Pure Play Wafer Foundry

TSMC started its wafer foundry business more than 30 years ago. Visionary management and creative engineering teams developed leading-edge process technologies and their reputation as trusted source for high-volume production. TSMC also recognized very early the importance of building an … Read More

Webinar: Design Methodologies for Next-Generation Heterogeneously Integrated 2.5/3D-IC Designs

I had the opportunity to preview the upcoming SemiWiki webinar titled: Design Methodologies for Next-Generation Heterogeneously Integrated 2.5/3D-IC Designs. John Park’s message, describing this powerful Cadence solution, really impressed me. That’s why I want to encourage you to register for it and join this SemiWiki … Read More

Accelerating 5G Design Innovation Through Simulation Workshop

DesignCon is coming up, kicking off the first of many industry conferences for the year. It’s at the Santa Clara Convention Center which is the best venue in Northern California. Not only is this a semiconductor crowd, it’s also a systems crowd covering chips, boards, and systems. More than 175 companies participate with an expected… Read More

HBM offers SOC’s dense and fast memory options

Dual in-line memory modules (DIMM’s ) with double data rate synchronous dynamic random access memory (DDR SDRAM) have been around since before we were worried about Y2K. Over the intervening years this format for provisioning memory has evolved from supporting DDR around 1995, to DDR1 in 2000, DDR2 in 2003, DDR4 in 2007 and DDR4… Read More

Cadence Expands Integrated Photonics Beachhead

In November of 2016, I made a bold statement that October 20, 2016 would stand as a watershed day in integrated photonics. The reason for this claim was that GLOBALFOUNDRIES proclaimed that integrated photonics was real and here to stay. The same week I wrote an article about Cadence Design Systems securing a photonic beachhead … Read More

Join the Multi-die IC session on April 21 at EDPS 2016 in Monterey, CA

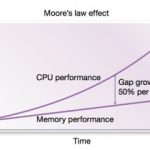

Following Moore’s Law down to 10 or even 7 nm labeled feature size demands US $ hundreds of millions of up-front investment, a very large design team and two or more years of development time. These parameters suggest that it only makes sense for very high volume applications to continue on the shrink path to increase SoCs’ functionalities.… Read More