You are currently viewing SemiWiki as a guest which gives you limited access to the site. To view blog comments and experience other SemiWiki features you must be a registered member. Registration is fast, simple, and absolutely free so please,

join our community today!

WP_Term Object

(

[term_id] => 14

[name] => Synopsys

[slug] => synopsys

[term_group] => 0

[term_taxonomy_id] => 14

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 784

[filter] => raw

[cat_ID] => 14

[category_count] => 784

[category_description] =>

[cat_name] => Synopsys

[category_nicename] => synopsys

[category_parent] => 157

[is_post] =>

)

WP_Term Object

(

[term_id] => 14

[name] => Synopsys

[slug] => synopsys

[term_group] => 0

[term_taxonomy_id] => 14

[taxonomy] => category

[description] =>

[parent] => 157

[count] => 784

[filter] => raw

[cat_ID] => 14

[category_count] => 784

[category_description] =>

[cat_name] => Synopsys

[category_nicename] => synopsys

[category_parent] => 157

[is_post] =>

)

I recently published a post on LinkedIn titled “Sometimes, you gotta throw it all out” in reference to the innovation process and getting beyond good to better. A prime example has crossed my desk: the new ProtoCompiler software for Synopsys HAPS FPGA-based prototyping systems.

Last week, I spoke with Troy Scott, product marketing… Read More

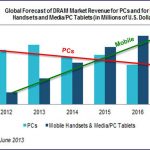

Welcome, LPDDR4!by Eric Esteve on 04-23-2014 at 3:46 amCategories: IP, Synopsys

Thanks to memory controller expert Marc Greenberg, Marketing Director for DDRn Controller IP with Synopsys, for this post “Qualcomm announces first application processor with LPDDR4 capability”. According with Marc, this Application Processor, the Snapdragon 810, is “the first product that I’m aware of that will use LPDDR4… Read More

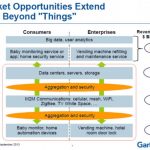

To further my quest to comprehend the latest trends in the semiconductor industry continues, I spent the morning with SEMI at the “The Silicon Valley Breakfast Forum: Internet of Things (IoT) – Driving the Microelectronics Revolution” seminar. I’m a big fan of the breakfast seminar concept. I’m up early anyway and it is … Read More

Sebastian Thrun gave a fascinating keynote at SNUG last week. It didn’t have that much to do with IC design but he discussed 3 projects that he had been involved with. Anyone would be happy to have just one of these projects on their resume but he has all these (and more).

The first is the Google self-driving car. This project actually… Read More

Bye-Bye DDRn Protocol?by Eric Esteve on 03-30-2014 at 11:34 amCategories: IP, Synopsys

In fact, this assertion is provocative, as the DDR4 protocol standard has just been released by JEDEC… after 10 years discussion around the protocol features. Yes, the first discussions about DDR4 have started ten years ago! Will DDR4 be used in the industry? The answer is certainly yes, and DDR4 will most probably be used for years.… Read More

Shipping a product with complete software support at official release is a lot more difficult than it sounds. Inevitably, there is less than enough hardware to go around, and what little there is has to fill the needs of hardware designers, test and certification engineers, software development teams, systems integration teams,… Read More

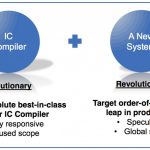

I have been at SNUG for the last couple of days. The big announcement is IC Compiler II. It was a big part of Aart’s keynote and Monday lunch featured all the lead customers talking about their experience with the tool.

The big motivation for IC Compiler II was to create a fully multi-threaded physical design tool that will scale… Read More

Digital verification engineers on SoC designs have adopted many techniques to help ensure first silicon success: using compiled simulators, constrained random test, simulation farms, SystemVerilog methodology, and self-checking testbenches. AMS verification has tended to be ad-hoc or sharply divided into separate analog… Read More

EDA start-up companies often have the advantage over established vendors by being able to start from scratch, instead of having to maintain some legacy code that no longer is competitive. But what happens when the established vendor decides to rewrite their IC implementation tools from scratch? In this case it’s good news,… Read More

Integration is often an underrated attribute of good tools, compared to raw performance and technology. But these days integration is differentiation (try telling that to your calculus teacher). Today at DVCon Synopsys announced Verification Compiler which integrates pretty much all of Synopsys’s verification technologies… Read More