Design-Technology Co-Optimization (DTCO) has been a foundational concept in semiconductor engineering for years. So, when Synopsys referenced DTCO in their April 2025 press release about enabling Angstrom-scale chip designs on Intel’s 18A and 18A-P process technologies, it may have sounded familiar—almost expected. But to dismiss it as “more of the same” would be to overlook just how far DTCO has come, and how dramatically Synopsys has elevated it. To gain deeper insights, I spoke with Prasad Saggurti, Executive Director of Product Management for Foundation and Security IP, and Ashish Khurana, Executive Director of R&D for Foundry Ecosystem at Synopsys.

DTCO: From Tactical Method to Strategic Enabler

In its earliest form, DTCO focused on adapting design techniques to meet the constraints of shrinking nodes. It was often a reactive, back-end effort to align standard cells and process rules with emerging technology limits. But as Moore’s Law encountered physical and economic headwinds, DTCO evolved into something far more comprehensive—an integrated, predictive approach to co-developing process and design in parallel.

Today, DTCO plays a central role in defining not just how chips are built, but what technologies are viable. And Synopsys, through its close collaboration with Intel, has taken it to a level where it’s shaping the future of Angstrom-era silicon.

DTCO Delivers Early on Intel 18A

The evolution of DTCO was in the spotlight during the 2025 Intel Foundry Direct Connect event. In an on-stage appearance alongside Intel CEO Lip-Bu Tan, Synopsys CEO Sassine Ghazi reached into his pocket, pulled out a chip, and held it up for the audience. That chip, he explained, was a Synopsys test chip built on Intel’s 18A process and had been produced a year earlier. It was proof that deep DTCO integration delivers real, early silicon results.

Such early silicon readiness would have been unthinkable in the traditional flow. It was made possible only because of a close, continuous DTCO collaboration between Synopsys and Intel—spanning process definition, tool enablement, IP development, and design methodology refinement.

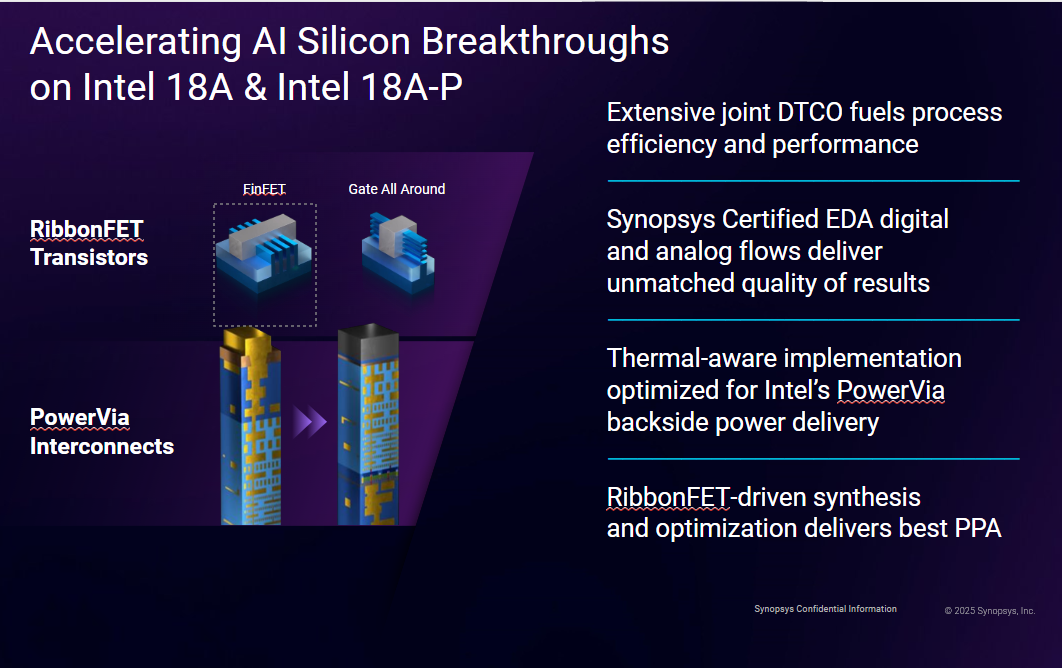

DTCO in Action: RibbonFET, PowerVia, and the Intel 18A Breakthrough

This transformation is best illustrated through the tangible gains achieved during the Intel 18A development. Synopsys worked closely with Intel to align their design tools with Intel’s RibbonFET transistor architecture, enabling reduction in timing closure cycles. This streamlined convergence and boosted productivity for design teams using the 18A platform.

At the same time, DTCO was instrumental in optimizing PowerVia, Intel’s backside power delivery system. By leveraging PowerVia-aware floorplanning within Synopsys’ place-and-route tools, the collaboration delivered improvement in power efficiency—a result of co-optimized IR drop management and floorplan restructuring enabled by early-stage modeling.

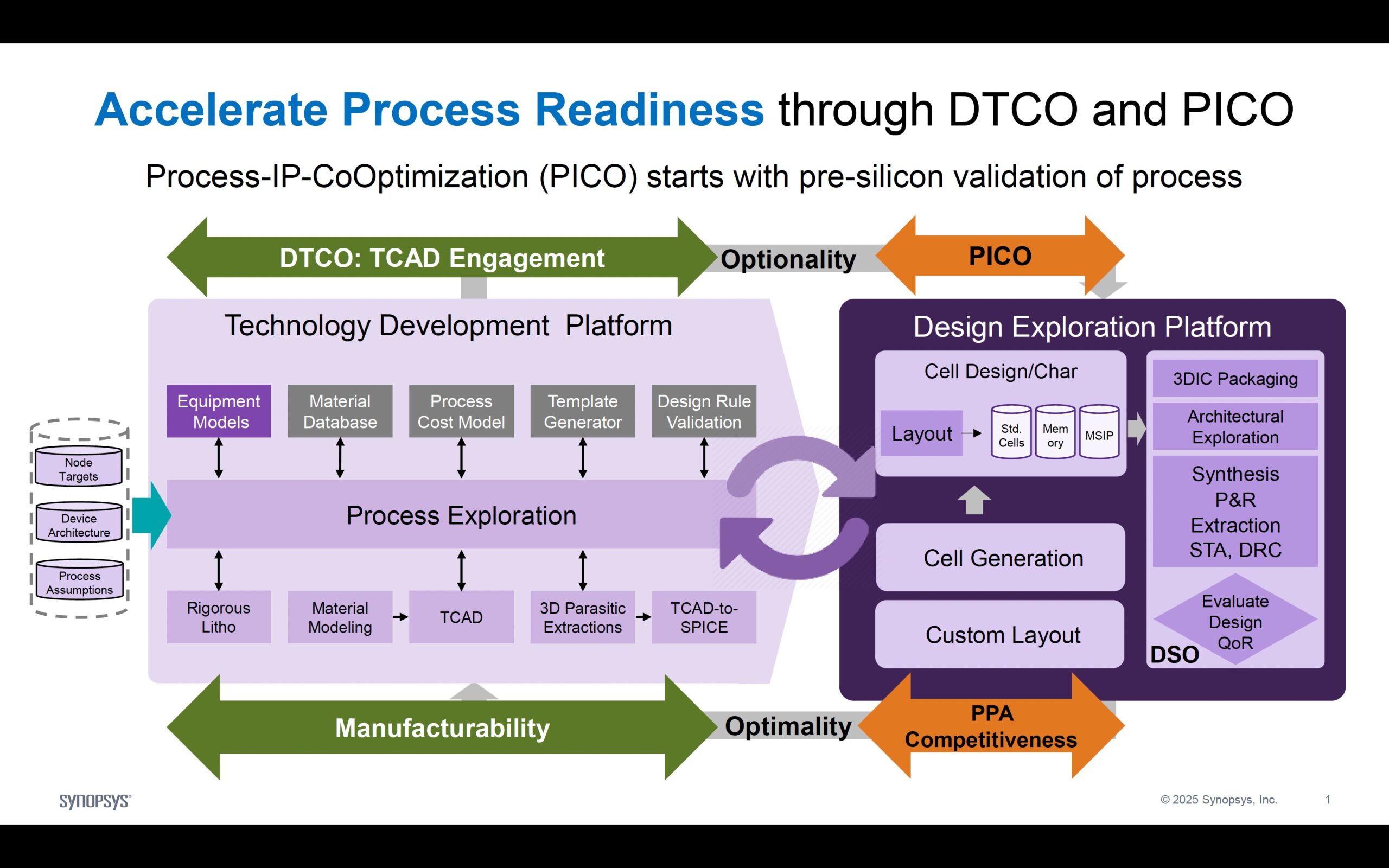

PICO: DTCO’s Evolution into Full-Stack Optimization

To manage this expanded scope, Synopsys introduced PICO—short for Process-IP-Co-Optimization. PICO represents a structured, pre-silicon flow that spans process assumptions, cell library development, IP integration, toolchain validation, and even 3DIC packaging studies. It ensures all components from transistor to tools are developed in tandem, under real-world constraints.

With PICO:

- TCAD simulations inform device models early in the cycle.

- Design rule validation occurs before masks are built.

- IP is co-architected with process and performance trade-offs in mind.

- CAD tools are aligned with structures like RibbonFET from the outset.

The Enablement Readiness Cycle: Getting to Market Faster

This all feeds into the enablement readiness cycle—a core strategy for delivering validated design flows, certified IP, and process-aligned methodologies in sync with foundry technology ramps. For Intel 18A, Synopsys’ tools and libraries were ready before silicon. This closed-loop cycle is central to achieving fast, low-risk product development at Angstrom-scale nodes.

Summary

Modern day DTCO is a competitive strategy for the Angstrom-scale era. With strategic collaborative partnerships between foundries and design-enablement ecosystem partners such as Synopsys, DTCO is a full-stack, front-loaded discipline capable of delivering real silicon on cutting-edge process nodes well ahead of schedule.

To learn more, visit Synopsys’ DTCO Solutions page.

Also Read:

Intel Foundry is a Low Risk Aternative to TSMC

Intel’s Foundry Transformation: Technology, Culture, and Collaboration

Intel’s Path to Technological Leadership: Transforming Foundry Services and Embracing AI

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.