At advanced nodes, design rules are necessarily more complex and restrictive. Although most of the time you can find a way to live with them, sometimes it’s necessary to seek a waiver from the foundry for a particular design feature. This involves documenting the feature, the design rules in question and the conditions under which… Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More

Captain America: Can Elon Musk Save America's Chip Manufacturing Industry?Intel has posted three consecutive years of falling…Read More WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More

WEBINAR: Reclaiming Clock Margin at 3nm and BelowAt 3nm and below, clock networks have quietly…Read More WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More

WEBINAR: HBM4E Advances Bandwidth Performance for AI TrainingThe rapid proliferation of LLMs and other AI…Read More Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More

Siemens Wins Best in Show Award at Chiplet Summit and Targets Broad 3D IC Design EnablementThe recent Chiplet Summit in Santa Clara was…Read More Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read More

Siemens Fuse EDA AI Agent Releases to Orchestrate Agentic Semiconductor and PCB DesignThough terminology sometimes get fuzzy, consensus holds that…Read MoreAn Affair to Remember: EDA’s 50th Anniversary

What an amazing night! I celebrated the 50[SUP]th[/SUP] anniversary of the industry I grew up in! With my beautiful wife at my side and a table full of friends we all went down memory lane, ate, drank, and then enjoyed the auction.

The tour of the new computer museum was amazing. I was learning so much up until the 1970’s, then … Read More

TSMC ♥ Synopsys (HSPICE)

In case you haven’t noticed, Synopsys has been in the press lately talking about their relationship with TSMC. Since I’m an internationally recognized industry expert they gave me a call for a briefing and I was happy to do it. Staying connected with the #1 EDA company is important and fun since I get to ask questions that most people… Read More

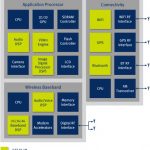

Tablets, smartphones & China still driving growth

Media tablets and smartphones have been the two most significant drivers of electronics and semiconductor growth for the last few years. Forecasts from two major market research firms indicate these devices will continue to be major drivers for the next few years. For 2013, Gartner and IDC (International Data Corporation) both… Read More

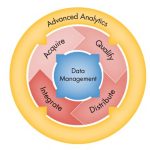

Webinar on IP Lifecycle Management

EDA and Semiconductor companies are offering new webinars almost every week of the year, so there’s always something worth learning about that only takes an hour of time. On November 5th there’s an interesting webinar planned on the topic of IP Lifecycle Management, hosted by Methodics. I blogged two weeks ago about,… Read More

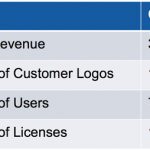

Kathryn: "Formal Will Dominate Verification"

At the Jasper Users’ Group meeting, Kathryn presented the state of Jasper. The numbers are impressive. The company has grown at a CAGR of over 35% since 2007, which is 6 times faster than EDA as a whole. They have been profitable at 15-20% EBITDA for 14 consecutive quarters.

Jasper is focused on engaging deeply with a small number… Read More

3DIC, the World Goes to…Burlingame

For the tenth year, the big 3DIC conference takes place in the Hyatt Regency at Burlingame (just south of San Francisco Airport). Officially it is 3D Architectures for Semiconductor Integration and Packaging or ASIP. This year there have already been some significant 3D announcements: TSMC’s 3D program, and Micron’s… Read More

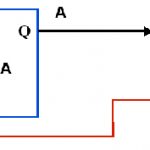

Hierarchical Clock Domain Crossing

One of the first blogs I wrote on SemiWiki was on clock domain crossing (CDC). I thought it was rather a specialized subject, a sort of minority interest. It turned out to be one of the most-read blogs I’ve written. Modern SoCs have lots of unrelated clocks, maybe hundreds, and so ensuring that signals going from one clock domain… Read More

Qualcomm start selling DSP IP core?…

In recent times semiconductor companies have revealed their intentions to license their in-house processor architectures for the first time – IBM want to license their Power CPU architecture, nVidia to license their GPU architecture. Most recently, a rumor has surfed: Qualcomm will license their DSP architecture. We should… Read More

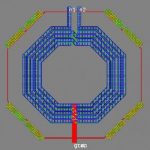

EM Solver and Visualization Essential for Device Design

In many designs, an on chip inductor is created as though it were simply a device with an L and a Q value. Of course this view would seem to make life simpler for designers and the tools they use. But in reality even a simple inductor is really a complex compound structure with many electromagnetic elements interacting in complex ways.… Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry