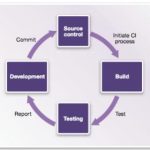

A familiar refrain in software development, as much as in hardware development, is that the size and complexity of projects continues to grow as schedules shrink and expectations of quality can increase dramatically. A common approach to managing this challenge in software programs is agile development practices and one aspect… Read More

IPLM: Future Forward Webinar May 19thStep into the future of semiconductor design management…Read More

IPLM: Future Forward Webinar May 19thStep into the future of semiconductor design management…Read More From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More

From Point Solutions to Agentic AI Ecosystems: Semiconductor Process Control Depends on Its PastAgentic AI is often presented as a revolutionary…Read More Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More

Panel Discission: Beyond Moore's Law and the Future of Semiconductor ManufacturingThe semiconductor industry is entering a post-Moore’s Law…Read More CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More

CEO Interview with Dave Kelf, CEO of Breker Verification SystemsIn the functional verification space, Breker Verification Systems stands…Read More RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read More

RISC-V: From Niche Architecture to Strategic FoundationAt the recent RISC-V Now by Andes conference,…Read MoreCEO Interview: Mike Wishart of efabless

This is the 12th in a series of interviews we will do with executives inside the fabless semiconductor ecosystem. Michael Wishart, efabless Chairman and CEO, retired from Goldman Sachs after thirty years covering the technology industry as an investment banker. Michael is currently on the board of Cypress Semiconductor and … Read More

Solido DA is One of Deloitte’s Fastest 50!

As a longtime EDA professional this really made my day. At a time where emerging EDA companies struggle for public validation, it warms my heart to see some very public recognition for an EDA job well done.

Deloitte, a leading Canadian professional financial services firm, announced the winners of their Technology Fast 50 program… Read More

Automobility: The Bot in a Box Boom

The Automobility event, which starts today ahead of the Los Angeles Auto Show, will be remembered for introducing the bot in a box. While Ford Motor Company President and CEO Mark Fields will take the stage this morning to tout Ford’s leadership in transforming transportation with new vehicle ownership models and mass produced… Read More

LRCX AMAT KLAC Update

Applied & Lam will be talking over the next 2 days, investors should/will focus on future growth, AMAT after display uptick & LRCX post the KLAM fail.

It’s no secret that most of the upside surprise in Applied’s recent reports were due to unusually large display orders from an industry even more cyclical than… Read More

Where hackers take their money – Casinos, Cryptocurrency, and Virtual Worlds

Cybercrime is reaching epidemic levels. Some estimates predict global annual cybercrime costs will reach $6 trillion by 2021. This includes the costs of security as well as the losses from thefts and fraud from successful attacks. Criminals are finding themselves in a position of having gained electronic assets but need to transform… Read More

Webinar: Improve Security For IoT Edge Devices With Custom SoCs

The only thing hotter than IoT on SemiWiki.com right now is IoT Security. In 2016 we saw a record amount of reported cyber security breaches with compelling consequences (US Presidential Election) and that trend will continue. The most recent DDoS (distributed denial of service) attacks using botnets on insecure IoT devices … Read More

eSilicon Demonstrates Potent Memory IP Evaluation Platform

With memories taking up in some cases over 50% of the area of many ASIC designs, their selection and implementation can affect everything from power and timing to the choice of packaging. As a result, the process of deciding among all the options for ASIC memories becomes time and energy intensive. Memory selection even affects … Read More

IoT Worms Could Spread Like Zombies

Security researchers recently created a proof-of-concept attack against Internet connected lightbulbs, causing breached devices to reach out and infect their neighbors. Propagation continues and spreads itself across the community. This hack highlights the insecurity in one of many IoT network protocols.

Researchers… Read More

#IoT: Internet of Tomatoes

In a previous post we looked at how we are going to scale #IoT deployments. The conclusion was that we needed the notions of trust and privacy to be in place for that to happen. In a follow up post, we looked at using a middle man to provider a broker platform that would mediate transactions between server side service applications and… Read More

The Semiconductor Growth Numbers are Insane but the Real World Doesn’t Tally!