ClioSoft is well known for their SoC design data management software SOS7 and more recently for their IP reuse ecosystem called designHUB. What is less known is how designHUB enables design teams to collaborate efficiently and better manage their projects by keeping everyone in sync during development. Not only does it provide… Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read MoreUsing a TCAD Tool to simulate Electrochemistry

In college I took courses in physics, calculus, chemistry and electronics on my way to earn a BSEE degree, then did an 8 year stint as a circuit designer, working at the transistor level and interacting with fab and test engineers. My next adventure was working at EDA companies in a variety of roles. As a circuit designer I knew that … Read More

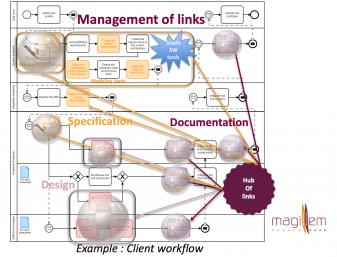

Design Data Intelligence

We have an urge to categorize companies, and when our limited perspective is of a company that helps with design, we categorize it as an EDA company. That was my view of Magillem, but I have commented before that my view is changing. I’m now more inclined to see them more as the design equivalent of a business intelligence organization… Read More

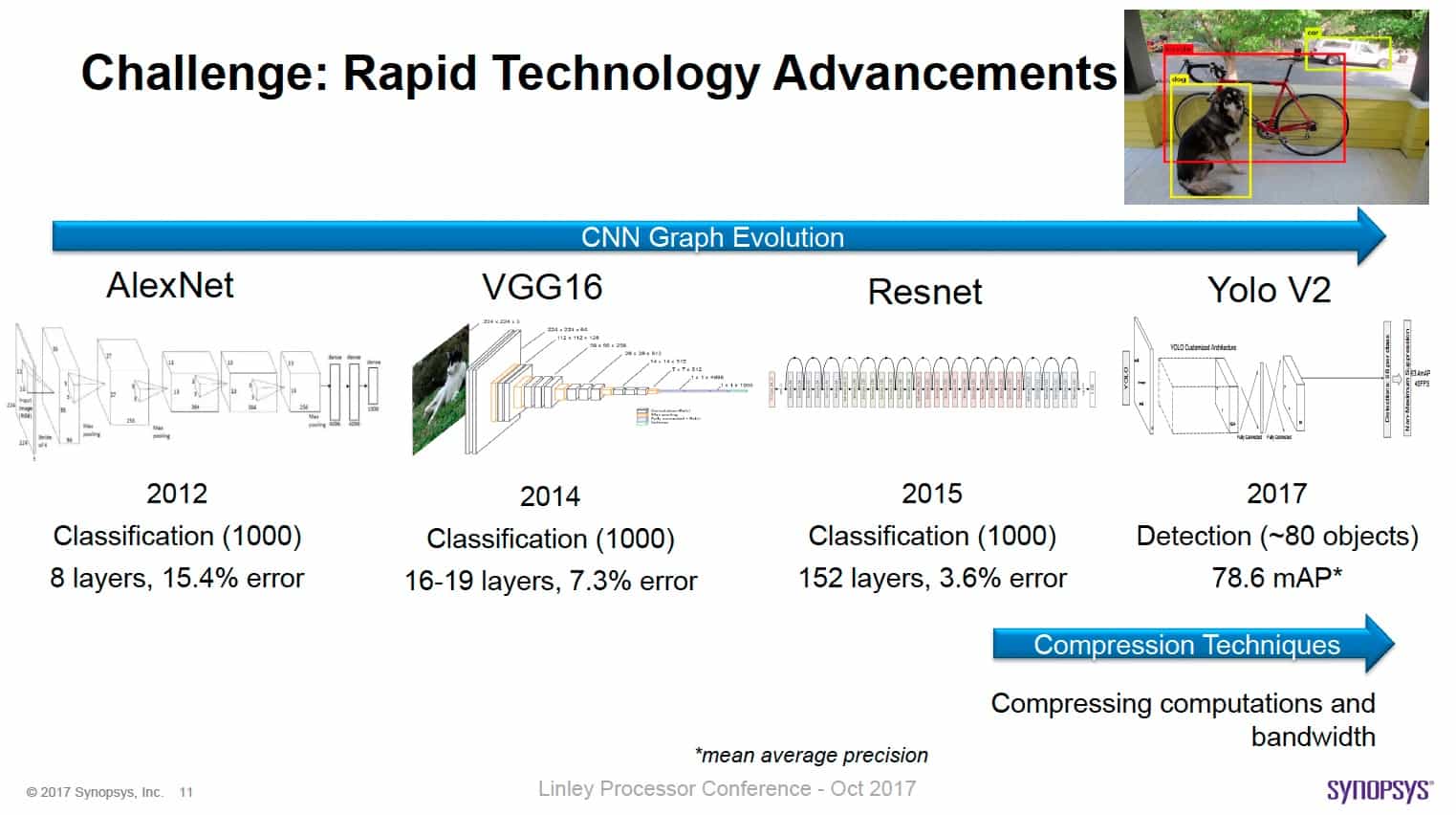

Synopsys discusses the challenges of embedded vision processing

Before the advent of convolutional neural networks (CNN), image processing was done with algorithms like HOG, SIFT and SURF. This kind of work was frequently done in data centers and server farms. To facilitate mobile and embedded processing a new class of processors was developed – the vision processor. In addition to doing a … Read More

Electronic Design for Self-Driving Cars Center-Stage at DVCon India

The fourth installment of DVCon India took place in Bangalore, September 14-15. As customary, it was hosted in the Leela Palace, a luxurious and tranquil resort in the center of Bangalore, and an excellent venue to host the popular event.

As reported in my previous DVCon India trip reports, the daily and evening traffic in Bangalore… Read More

1st Annual International Conference, Semiconductors ISO 26262

When we talk about the promise of ADAS and autonomous cars then along the way we also hear about this functional safety standard called ISO 26262 which semiconductor companies all pay close attention to. I recently learned about a new conference called Semiconductors ISO 26262, scheduled for December 5-7 in Munich, Germany. The… Read More

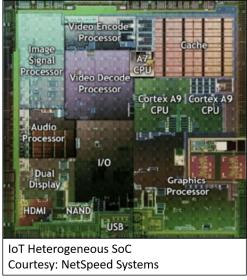

ARM Security Update for the IoT

Despite all the enthusiastic discussion about security in the IoT and a healthy market in providers of solutions for the same, it is difficult to believe that we are doing more than falling further behind an accelerating problem. Simon Segars echoed this in his keynote speech at ARM TechCon this year. The issue may not be so much in… Read More

The perfect pairing of SOCs and embedded FPGA IP

In life, there are some things that just go together. Imagine the world without peanut butter and jelly, eggs and potatoes, telephones and voicemail, or the internet and search engines. In the world of computing there are many such examples – UARTS and FIFO’s, processor cores and GPU’s, etc. Another trait all these things have is… Read More

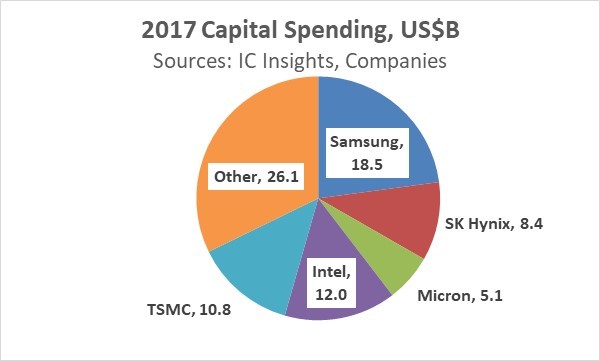

Capex Driving Overcapacity?

Semiconductor capital expenditures (cap ex) in 2017 will increase significantly from 2016. In August, Gartner forecast 2017 cap ex growth of 10.2% and IC Insights projected 20.2% growth. SEMI expects spending on semiconductor fabrication equipment will increase 37%. Cap ex growth is primarily driven by increased capacity… Read More

Nvidia’s Pegasus Putsch!

There hasn’t been this much excitement in Munich since the 1920’s. Nvidia’s great pivot was on display at the GPU Technology Conference Munich 2017. Digital dashboards are out and robotaxis are in as Nvidia narrows its focus on the tip of the automotive industry disruption spear.

To be clear, Nvidia is triangulating on the automotive… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center