For years, the lords of Lyft and Uber have declaimed their intention to vanquish car ownership and displace public transportation. It really was as simple and as blunt as that. For sure there would be collateral damage including rental car companies and taxi operators and millions of under-compensated drivers – but the bottom

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More

Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read More

CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read MoreDVCon 2020 Virtual Follow-Up Conference!

As most of you know DVCon 2020 was our first conference to be cut short by the Pandemic. SemiWiki bloggers Bernard Murphy, Mike Gianfagna, and I were there with full schedules but at the last minute it was called off. It really was an eerie feeling, the emptiness of it all.

The rest of our EDA live events followed suit and went virtual … Read More

Talking Sense with Moortec: Staying on the right side in worst case conditions – Power (Part 1)

In this first part of a 2-part blog series, we look at defining worst case conditions, focusing specifically on device power.

With great power, comes great responsibility…

With each new technology node especially FinFET, the dynamic conditions within a chip are changing and becoming more complex in terms of process speeds, thermal… Read More

The Moving Target Known as UPF

As if engineers did not have enough difficulty just getting everything right so that their designs are implemented functionally correct, the demands of lowering power consumption require changes that can affect functionality and verification. Techniques such as power gating, clock gating, mixed supply voltage, voltage … Read More

Cruise Controlling Its Destiny

The Information tells us that General Motors’ Cruise Automation self-driving car unit has acquired automotive radar maker Astyx. The move can be seen as a simple defensive move to preserve access to valuable radar technology along the path to realizing Cruise’s vision of a robotaxi infused future.

There are a variety

Cadence Adds “Always On” to vManager Verification Management with Distributed and Cloud Access

Cadence vManager™ Verification Management provides what the company describes as metric-driven signoff. Anyone who has been through the tapeout process for a complex SoC knows the perils of verification sign-off. How much of the chip has been verified? What’s left to do? Will all be ready when the tapeout deadline arrives? … Read More

Where’s the Value in Next-Gen Cars?

Value chains can be very robust and seemingly unbreakable – until they’re not. One we’ve taken for granted for many years is the chain for electronics systems in cars. The auto OEM, e.g. Toyota, gets electronics module from a Tier-1 supplier such as Denso. They, in turn, build their modules using chips from a semiconductor chip maker… Read More

Fractal CEO Update 2020

Rene Donkers, the company’s Co-founder and CEO, started his EDA career at Sagantec where he became responsible for world wide customer support and operations management. Ten years ago, Rene and a handful of people noticed a need in the design community for a standardized (portable) IP Validation approach to replace internal… Read More

Webinar: Optimize SoC Glitch Power with Accurate Analysis from RTL to Signoff

I had the opportunity to preview an upcoming webinar from Synopsys on SoC Glitch Power – what it is and how to reduce it. There is some eye-opening information in this webinar. Glitch power is a bigger problem than you may think and Synopsys has some excellent strategies to help reduce the problem. The webinar is available via replay… Read More

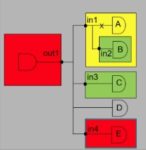

What’s At the Center of Your SoC Design Process?

I love starting a new project from scratch, because there’s that optimistic feeling of having no constraints and being able to creatively express myself and get the job done right this time. For SoC designs today there are teams of engineers and maybe a program manager plus a marketing person that define the features, budget… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center