Heterogeneous integration (HI) is a general term used to represent the diverse possibilities for die technology incorporated into advanced 2.5D/3D packaging. At the recent International Electron Devices Meeting (IEDM) in San Francisco, a team from Synopsys and IC Knowledge presented data from analyses of future potential… Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More

Synopsys Advances Hardware Assisted Verification for the AI EraAt the 2026 Synopsys Converge Event, Synopsys announced…Read More Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More

Chemical Origins of Environmental Modifications to MOR Lithographic ChemistryIn the pursuit of advanced extreme ultraviolet (EUV)…Read More Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More

Post-Silicon Validating an MMU. Innovation in VerificationSome post-silicon bugs are unavoidable, but we’re getting…Read More Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More

Securing UALink in AI clusters with UALinkSec-compliant IPA classic networking problem is securing connections with…Read More2D NoC Based FPGAs Valuable for SmartNIC Implementation

Smart network interface cards (SmartNICs) have proven themselves valuable in improving network efficiency. According to Scott Schweitzer, senior product manager at Achronix, it has been shown that SmartNICs can relieve up to – and perhaps beyond – 30% of the host processor’s loading. SmartNICs started out taking… Read More

Methodology for Aging-Aware Static Timing Analysis

At the recent Design Automation Conference, Cadence presented their methodology for incorporating performance degradation measures due to device aging into a static timing analysis flow. [1] (The work was a collaborative project with Samsung Electronics.) This article reviews the highlights of their presentation.

Background… Read More

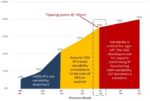

Delivering Systemic Innovation to Power the Era of SysMoore

With the slowing down of Moore’s law , the industry as a whole has been working on various ways to maintain the rate of growth and advancements. A lot has been written up about various solutions being pursued to address specific aspects. The current era is being referred to by different names, SysMoore being one that Synopsys uses.… Read More

DAC 2021 – Taming Process Variability in Semiconductor IP

Tuesday at DAC was actually my very first time attending a technical session, and the presentation from Nebabie Kebebew, Siemens EDA, was called, Mitigating Variability Challenges of IPs for Robust Designs. There were three presentations scheduled for that particular Designer, IP and Embedded Systems track, but with the COVID… Read More

5 Talks on RISC-V

Veriest recently hosted a webinar focusing on RISC-V as a forerunner of ongoing open-source revolution in chip design. Speakers were distinguished professionals from industry and academia. Webinar covered topics from market trends to open-source hardware initiatives, tools and methodologies.

Zvonimir Bandić: RISC-V … Read More

Podcast EP54: Ventana Micro, RISC-V, HPC and Chiplets

Dan is joined by Balaji Baktha, founder and CEO of Ventana Micro. Balaji explores the application of RISC-V in high-performance applications and the specific advantages of a chiplet-based approach.

RISC-V Summit Panel: https://www.youtube.com/watch?v=duZaAhWxhWM

The views, thoughts, and opinions expressed in these… Read More

AI for EDA for AI

I’ve been noticing over the last few years that electronic design automation (EDA) vendors just love to talk about artificial intelligence (AI) and machine learning (ML), sometimes with deep learning (DL) and neural networks tossed in as well. It can get a bit confusing since these terms are used in two distinct contexts. The first… Read More

Scalable Concolic Testing. Innovation in Verification

Combining simulation and symbolic methods is an attractive way to excite rare branches in block-level verification, but is this method really scalable? Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO) and I continue our series on research ideas. As always,… Read More

Cut Out the Cutouts

In 2014, many of the customers that my team and I supported in North America were still using HFSS 3D to model boards and packages. These customers were content with that interface, able to get their models setup quickly, and were okay with the solution times because when HFSS gave them an answer, they knew it was the right answer. I … Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era