SuperSpeed USB specification was released in November 2008! Even if we can see USB 3.0 powered peripherals shipping now, essentially external HDD, connected to PC equipped with Host Bus Adaptors (as PC chipset from Intel or AMD were not supporting USB 3.0), it will take up to the second quarter of 2012 before PC will be shipped with… Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More

Samtec’s Strong Presence at embedded world 2026The embedded world Exhibition & Conference recently concluded.…Read More Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More

Webinar – How to Reclaim Margin in Advanced NodesThis informative webinar discusses a significant issue that…Read More Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More

Alchip’s Leadership in ASIC Innovation: Advancing Toward 2nm Semiconductor TechnologyAlchip Technologies has recently reported significant progress in…Read More CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read More

CapEx Up for Foundry, MemorySemiconductor Intelligence estimates total semiconductor industry capital spending…Read MoreSoC Realization: Let’s Get Physical!

If you ask design groups what the biggest challenges are to getting a chip out on time, then the top two are usually verification, and getting closure after physical design. Not just timing closure, but power and area. One of the big drivers of this is predicting and avoiding excessive routing congestion, which is something that … Read More

Amazon’s Kindle Fire Spells Trouble for nVidia, Qualcomm and Intel

With the introduction of the Kindle Fire, it is now guaranteed that Amazon has the formula down for building the new, high volume mobile platform based on sub $9 processors. In measured fashion, Amazon has moved down Moore’s Law curve from the initial 90nm Freescale processor to what is reported to be TI’s OMAP 4 in order to add the … Read More

AMS Verification: Speed versus Accuracy

I spent Thursday Sept. 22 at the first nanometer Circuit Verification Forum, held at TechMart in Santa Clara. Hosted by Berkeley Design Automation (BDA), the forum was attended by 100+ people, with circuit designers dominating. I spoke with many attendees. They were seeking solutions to the hugely challenging problems they … Read More

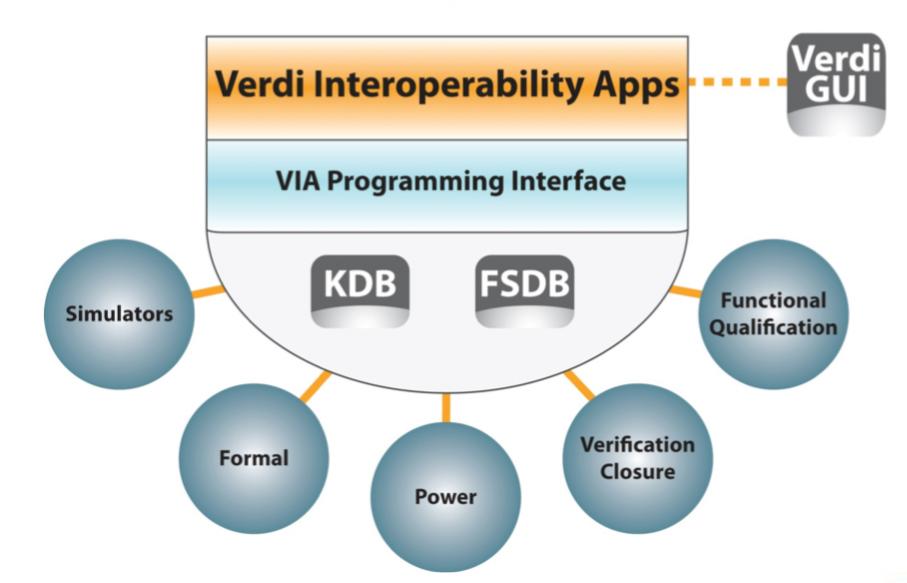

Verdi: there’s an App for that

Verdi is very widely used in verification groups, perhaps the industry’s most popular debug system. But users have not been able to access the Verdi environment to write their own scripts or applications. This means either that they are prevented from doing something that they want to do, or else the barrier for doing it is… Read More

Making Money With Cramer? Don’t Count on it!

Investing with Cramer is a crap shoot. By Cramer, I mean the Mad Money TV show, and Action Alerts PLUS from thestreet.com. Cramer is certainly a smart guy and knows his stuff, but don’t think following his investment strategy is necessarily a winner. He constantly maintains that you can beat the averages by picking individual… Read More

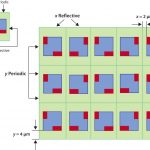

Memory Cell Characterization with a Fast 3D Field Solver

Memory designers need to predict the timing, current and power of their designs with high accuracy before tape-out to ensure that all the design goals will be met. Extracting the parasitic values from the IC layout and then running circuit simulation is a trusted methodology however the accuracy of the results ultimately depend… Read More

Introducing TLMCentral

Way back in 1999 the open SystemC initiative (OSCI) was launched. In 2005 the IEEE standard for SystemC (IEEE1666-2005 if you are counting) was approved. In 2008, TLM 2.0 was standardized (transactional level models), making building virtual platforms using SystemC models easier. At least the models should be play nicely together,… Read More

Analog IP Design at Moortec

Stephen Crosher started up Moortec in the UK back in 2005 with the help of his former Zarlink co-workers and they set to work offering AMS design services and eventually created their own Analog IP like the temperature sensor shown below:

We spoke by phone last week about his start-up experience and how they approach AMS design.… Read More

Samsung versus Apple and TSMC!

Apple will purchase close to eightBILLION dollars in parts from Samsung for the iSeries of products this year alone, making Apple Samsung’s largest customer. Samsung is also Apple’s largest competitor and TSMC’s most viable competitive foundry threat so it was no surprise to see Apple and TSMC team up on the next generations of… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center