Jussi-Pekka Penttinen is the chief executive officer, chief technical officer, and cofounder of Vexlum Ltd, an advanced laser technology company. With more than 15 years of experience, he is a leading researcher in the field of Vertical External Cavity Surface Emitting Laser (VECSEL) and successfully commercialized the technology.… Read More

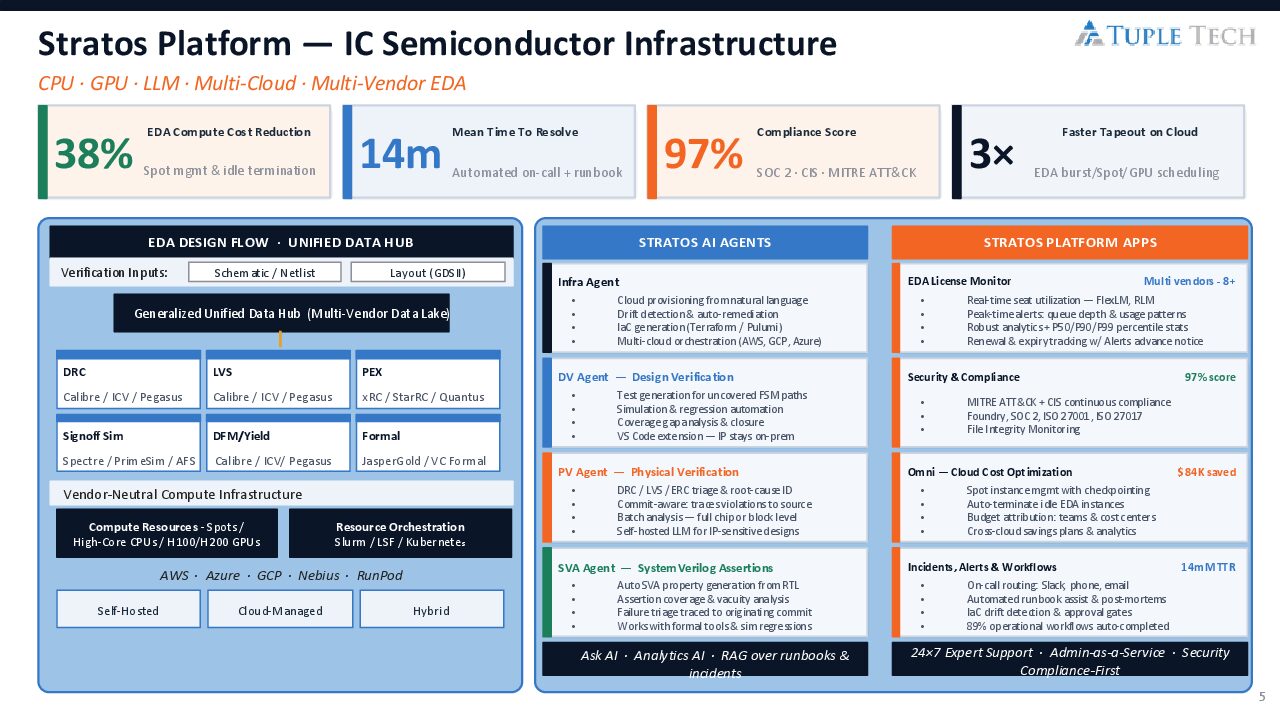

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read More

Rethinking ECAD IT Infrastructure: From Fragmentation to an Engineering PlatformThe semiconductor industry is entering a new phase…Read MorePodcast EP337: The Importance of Network Communications to Enable AI Workloads with Abhinav Kothiala

Daniel is joined by Abhinav Kothiala, a principal product manager for the Synopsys Ethernet IP portfolio. He has over 12 years of experience across engineering and product management, spanning SoC design, functional verification, and building wireless connectivity platforms and IoT products. He also holds two patents in… Read More

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center

At the TERAFAB launch event in Austin on March 21, Elon Musk made a prediction that would have sounded like science fiction a decade ago—and may still: roughly 80 percent of AI compute will eventually move off-planet.

The argument is straightforward once you accept his premises. Earth-based data centers face three hard constraints—land,… Read More

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era

As semiconductor technology advances into increasingly complex and expensive process nodes, the economic and technical risks associated with ASIC design have grown dramatically. At advanced nodes such as Intel 18A, the cost of a single design error can escalate into tens of millions of dollars, compounded by months of delay.… Read More

Synopsys Advances Hardware Assisted Verification for the AI Era

At the 2026 Synopsys Converge Event, Synopsys announced a broad set of new products and platform upgrades, with its hardware-assisted verification (HAV) announcement emerging as a key highlight within that lineup. A key aspect of this announcement was moving beyond a hardware centric model to a more scalable, programmable … Read More

Chemical Origins of Environmental Modifications to MOR Lithographic Chemistry

In the pursuit of advanced extreme ultraviolet (EUV) lithography for high-NA patterning, metal oxide resists (MORs) offer significant promise but face challenges like critical dimension (CD) variation due to atmospheric interactions. Presented at SPIE Advanced Lithography + Patterning 2025 by Kevin M. Dorney and colleagues… Read More

Post-Silicon Validating an MMU. Innovation in Verification

Some post-silicon bugs are unavoidable, but we’re getting better at catching them before we ship. Here we look at a method based on a bare-metal exerciser to stress-test the MMU. Paul Cunningham (GM, Verification at Cadence), Raúl Camposano (Silicon Catalyst, entrepreneur, former Synopsys CTO and lecturer at Stanford, EE292A)… Read More

Securing UALink in AI clusters with UALinkSec-compliant IP

A classic networking problem is securing connections with encrypted data, but implementing strong encryption algorithms at wire speeds can limit performance. However, introducing blazing-fast connectivity without an encryption strategy leaves systems vulnerable. The architects in the UALink Consortium, including … Read More

GTC 2026: Agentic AI for Semiconductor Design and Manufacturing

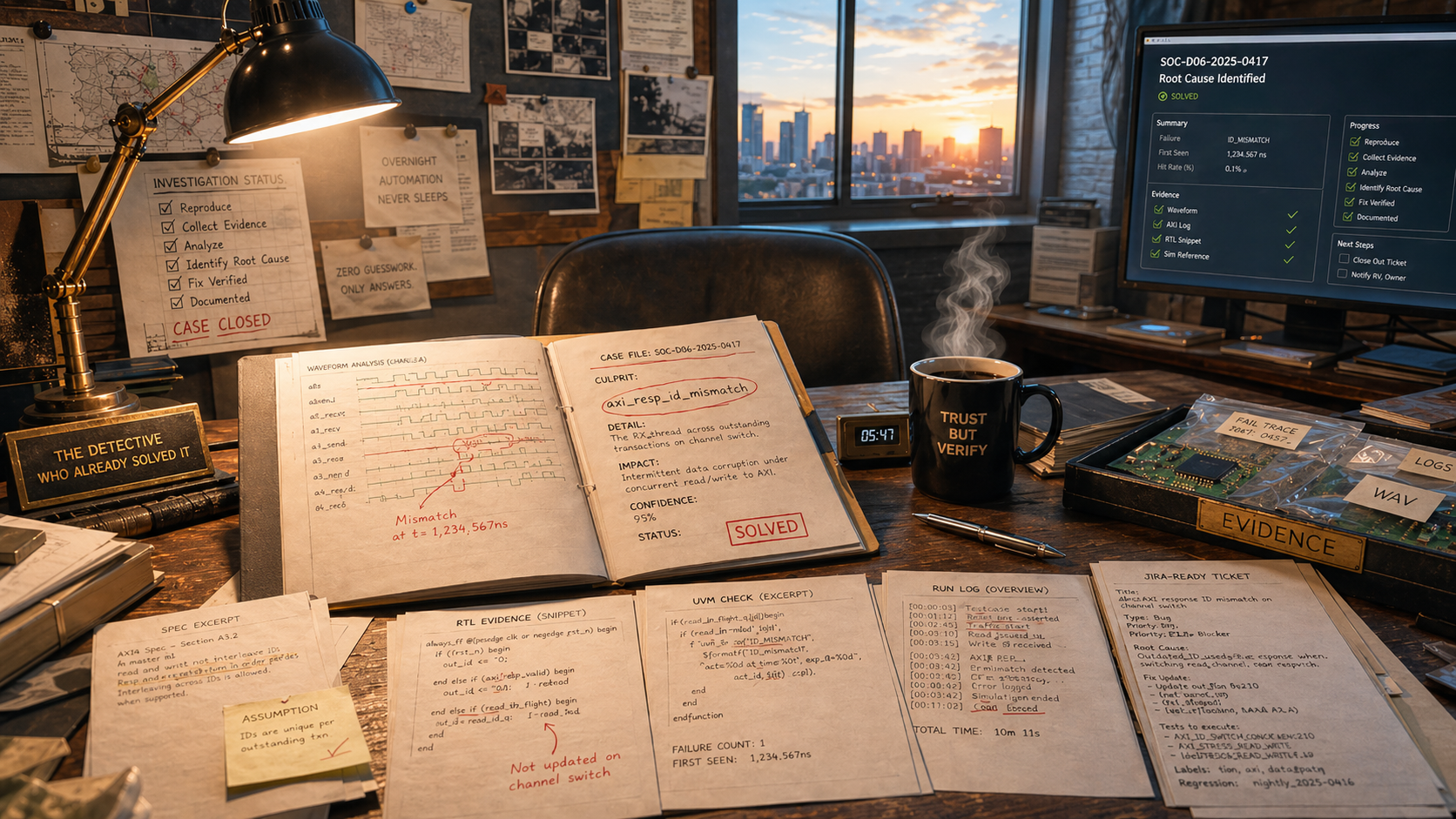

Trust in Verification with AI

These are stressful times in functional verification. We are being pushed to more aggressively embrace AI-based automation, knowing we will continue to be held accountable for quality of results. Verification misses could upend careers, maybe enterprises. It is tempting to believe that sanity will prevail and we will ultimately… Read More

Siemens U2U 3D IC Design and Verification Panel