RISC-V has emerged as a cornerstone of modern computing, offering an open-source alternative to proprietary designs like ARM and x86. Free from licensing fees and highly extensible, RISC-V powers everything from IoT devices to AI accelerators, with over 13 billion cores shipped globally. Annual RISC-V Summits, organized by RISC-V International, serve as vital hubs for innovation, fostering collaboration among engineers, academics, and industry leaders. In 2025, these events have spotlighted advancements in AI, automotive, and high-performance computing, with Andes Technology standing out as a key architect of the RISC-V ecosystem.

The year kicked off with the RISC-V Summit Europe in Paris (May 12-15), where attendees explored Europe’s burgeoning RISC-V landscape. Amid keynotes on industrial adoption and academic research, the summit emphasized single-track sessions blending invited talks, exhibitions, and hands-on demos. A highlight was the call for contributions, which prioritized topics like security frameworks and vector extensions, reflecting RISC-V’s push into edge AI.

Transitioning to Asia, the fifth RISC-V Summit China convened in Shanghai’s Zhangjiang Science Hall (July 16-19), focusing on supply chain integration and domestic innovation. With China’s massive semiconductor investments, sessions delved into scalable SoCs for 5G and smart manufacturing, underscoring RISC-V’s geopolitical resilience.

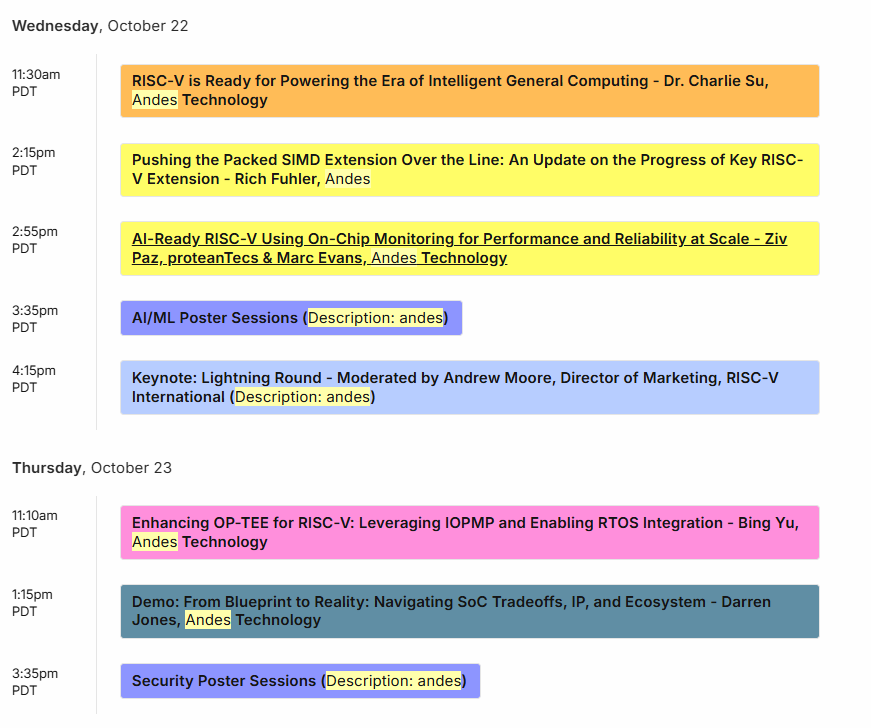

Next is the RISC-V Summit North America in Santa Clara, California (October 22-23). Hosted at my favorite location, the Santa Clara Convention Center, it promises content from industry leaders Synopsys, Andes Technology, Siemens, Breker, CAST, SiFive, Arteris IP, and others.

Expect deep dives into automotive-grade RISC-V, inspired by Infineon’s inaugural Automotive RISC-V Ecosystem Summit in July, which gathered stakeholders to tackle ISO 26262 compliance for ADAS systems. Collectively, these summits have accelerated ecosystem growth, with live demos of Linux-booting prototypes and certification initiatives ensuring interoperability.

Andes Technology, a founding Premier member of RISC-V International and a powerhouse in embedded CPU IP, hosts eight different activities this year including a keynote, talks, and poster sessions:

Since 2005, Andes has shipped billions of cores, blending proprietary AndeStar V5 enhancements with RISC-V compliance for optimal performance-per-watt. Their portfolio spans 32/64-bit processors: the D25F for low-power DSP tasks, the AX25MP for symmetric multiprocessing with L2 cache coherence, and the A25 for general-purpose efficiency. A standout is the NX27V, a 64-bit vector processor with a five-stage pipeline, tailored for AI workloads under the latest RISC-V specs.

Andes’ summit activities amplify their influence. At Europe 2025, they unveiled AI-centric demos, including RISC-V IP powering Meta’s accelerators and ASPEED’s 360-degree video processors—showcasing real-time spherical imaging for conferencing. In China, Andes collaborated with S2C on prototyping tools, accelerating SoC tape-outs. Their own Andes RISC-V CON series—debuting in Silicon Valley (April) and Seoul (September)—complements these, with sessions on security and application processors.

Looking ahead, Andes eyes the North America Summit for announcements on U.S.-designed high-performance cores via their Condor Computing arm, established for ultra-scalable IP with Linux emulation already validated and shipments imminent. Partnerships, like the tie-up with DeepComputing for QiLai SoCs featuring quad-core AX45MP clusters, further embed Andes in AI hardware.

Andes’ ethos democratizing compute through open standards mirrors RISC-V’s mission, driving adoption in EVs, data centers, and beyond. As summits evolve, expect Andes to lead on vectorized AI and secure extensions, propelling RISC-V toward trillion-core ubiquity. In an era of chip wars, these gatherings remind us: collaboration, not silos, fuels progress.

Bottom line: In my experience this conference is well attended, deep in content and provides excellent RISC-V networking opportunities. I hope to see you there, it would be a pleasure to meet you.

Also Read:

Podcast EP309: The State of RISC-V and the Upcoming RISC-V Summit with Andrea Gallo

Beyond Traditional OOO: A Time-Based, Slice-Based Approach to High-Performance RISC-V CPUs

Andes Technology: Powering the Full Spectrum – from Embedded Control to AI and Beyond

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.