I use social media 7 days a week and while at DAC I received a message from Herve Guegan on my LinkedIn account where he basically said, “Hey, go check out Asygn at DAC, they do analog macro models.”

Herve and I worked together at Mentor Graphics, where he lead the Eldo development team (SPICE simulator) and I marketed Mach TA (Fast SPICE simulator).

Based on that connection and history, it was an easy decision to visit Asygn at DAC on Tuesday.

Notes

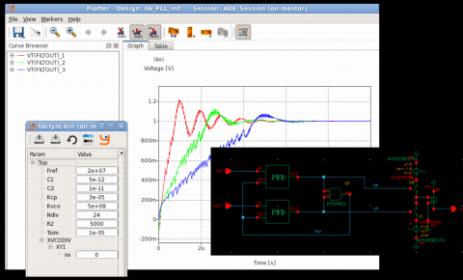

Time domain simulator called Tactyle that uses analog behavioral models in a SPICE syntax to model analog behavior. You can use any schematic capture – Cadence, Mentor, Tanner (not synopsys yet).

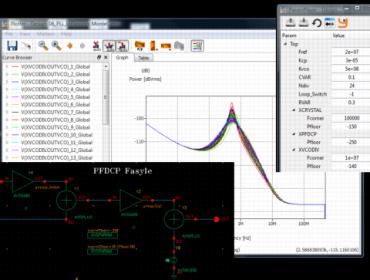

Analysis – frequency and transient domain (combined with noise sources)

The frequency domain simulator is called Fasyle.

Visualize – own waveform viewer

Simulation – can be interactive mode

Plotting – any node in your circuit (.PRINT, .PLOT)

Library of macro models has about 60 models so far. Philosophy is to provide simple models that can be combined to create anything you want to design.

All the primitives have a Verilog A equivalent, so you can switch to use any Verilog A simulator.

Tactyle – simulator for Time domain. Speed of 100X over Verilog A.

Fasyle – frequency domain simlator.

Customers – Freescale in France, CEA in France.

$60K for Tactile, 1 year floating license.

Licensing – either using generic simulator, or a custom GUI per customer. Created a pixel simulator as well for one client.

Factory – they can create models in C++.

Some blocks you can write C code as well using their API.

I get compiled analog models, not the source code.

Co-simulates with Verilog or System C (all major EDA vendors) using the standard API.

Platforms: Linux, WIndows

Because their simulator doesnt have to do transistors it is much faster than any SPICE or Verilog A simulator.

Summary

Writing models for AMS is a chore and has a learning curve, so it seems natural to simply place analog building blocks in a schematic capture environment and set the parameters. The approach by Asygn looks viable and it will compete with AMS libraries and simulators from Mentor Graphics, Cadence and Synposys.

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era