Ivo Bolsens, the CTO of Xilinx, is giving the opening keynote at the Electronic Design Process Symposium (EDPS) in Monterey on Thursday and Friday this coming week. The title of his keynote is The All Programmable SoC – At the Heart of Next Generation Embedded Systems. He covers a lot of ground but the core of his presentation is about how designing systems in FPGAs is moving up to the C level.

Some background. A couple of years ago Xilinx acquired AutoESL, a high-level synthesis (HLS) company. And the only one to actually make a return to their investors with that acquisition.

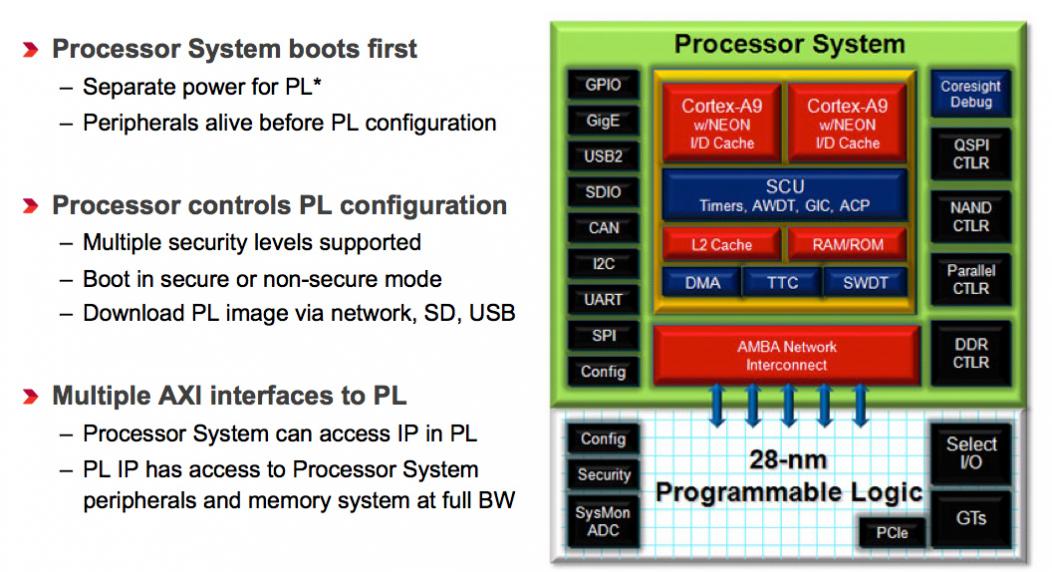

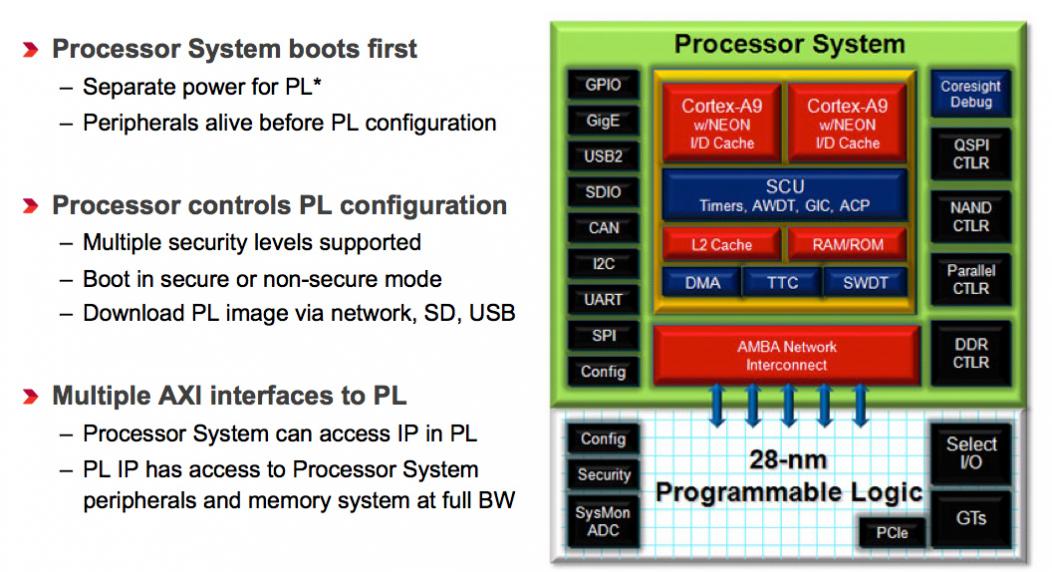

A modern Xilinx FPGA with a multi-core embedded ARM allows design to be thought of a bit differently. Instead of thinking of the FPGA as a sort of remote peripheral ,which is the old way of doing things, it is the heart of whatever system the SoC is implementing. The ARM and the FPGA fabric are tightly integrated. This has some big advantages, not least that the ARM can power up first and then can configure the FPGA. But the big change is that instead of thinking of the FPGA fabric as hardware, it can really be thought of as an accelerator for various parts of the software.

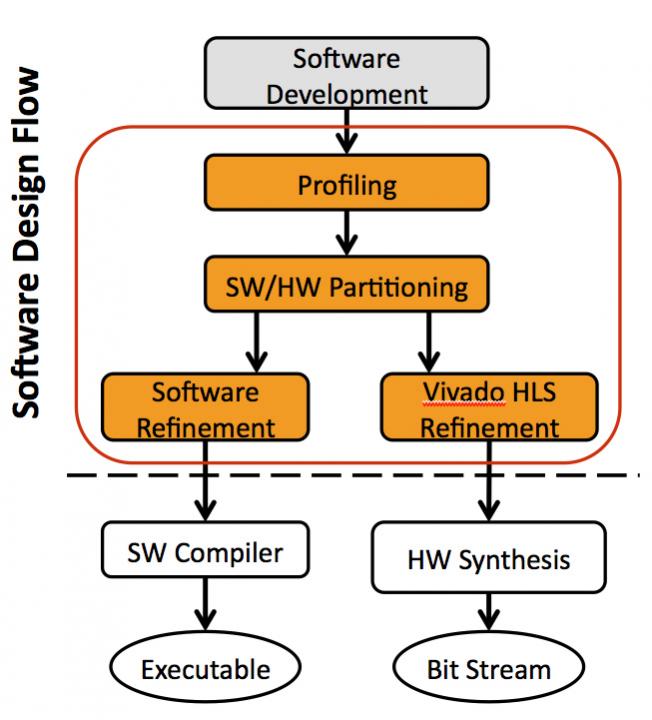

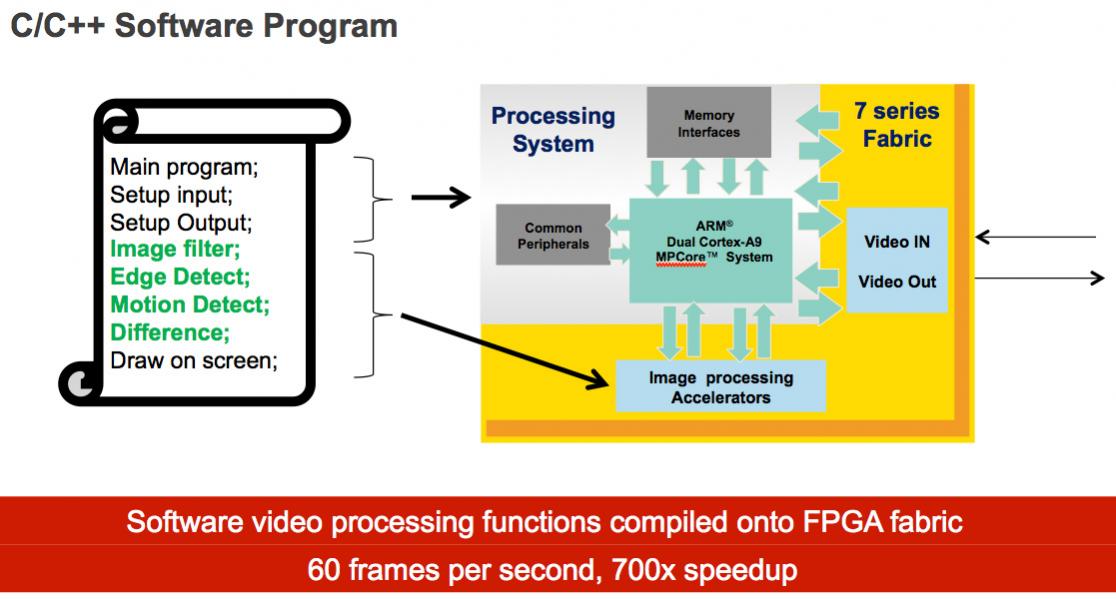

So the design flow is to use profiling to decide what to implement in software and what in FPGA fabric, and then the software to be implemented as software is compiled using a regular C (or C++) compiler, and the software that is to be implemented as hardware is compiled with Vivado HLS (today’s descendent of AutoESL’s AutoPilot). All the interfaces (operating systems, software stubs and links back to the ARM buses) are generated automatically.

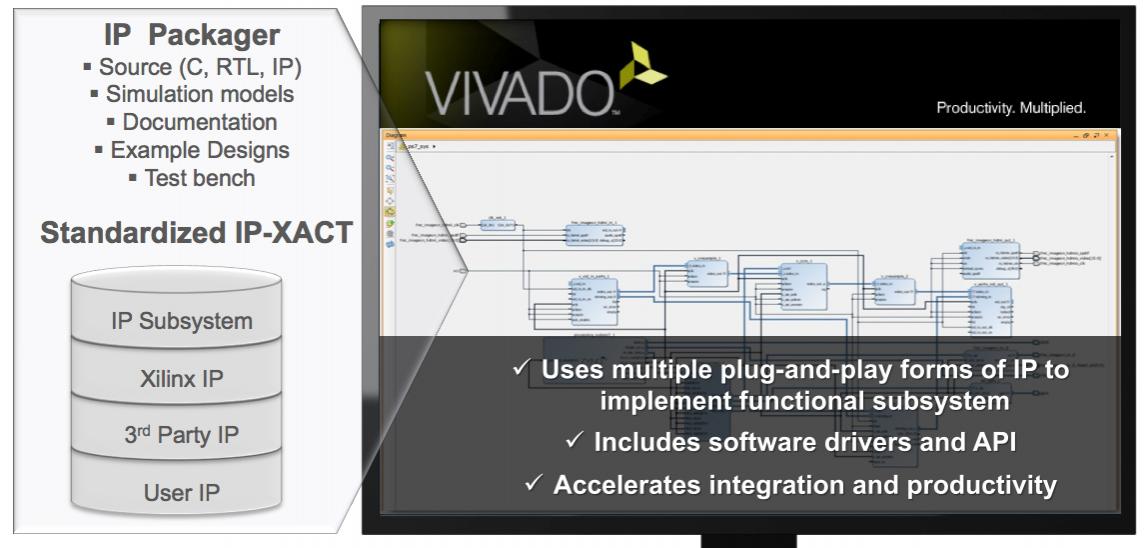

Of course, a modern SoC doesn’t just start from thousands of lines of Verilog (or C), it requires IP and to build FPGA-based programmable SoCs requires an IP library and IP integration tools. FPGA design has much smaller teams and often much less skilled so this has to be more straightforward that in the IP assembly world of a modern (non-FPGA) SoC.

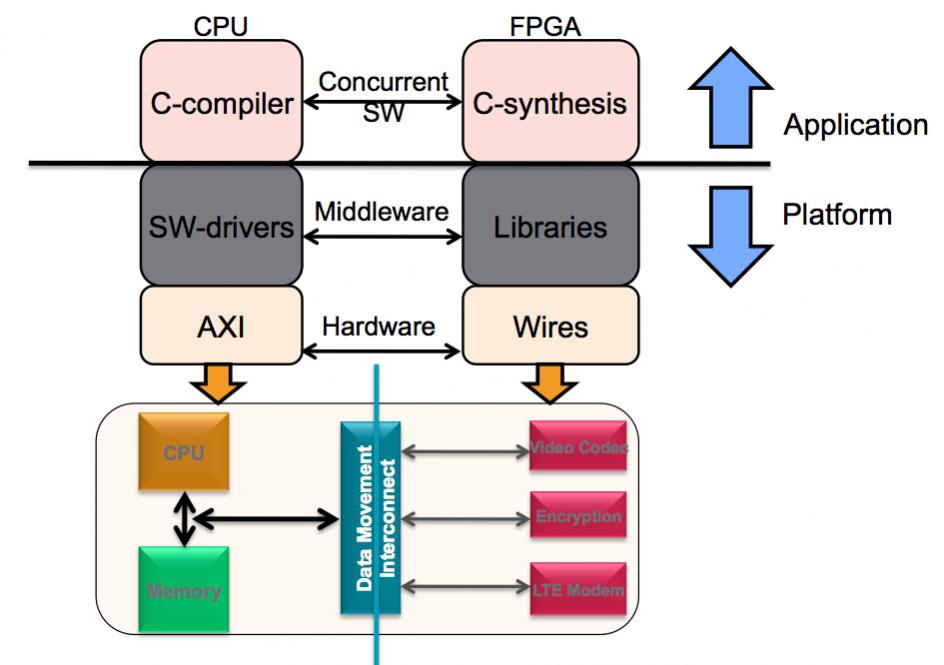

Putting it all together leads to a system with everything tied together so that the “inner loops” of the algorithms are implemented using the FPGA fabric and the rest of the system is implemented in software running on the ARM Cortex processor cores.

Putting it all together leads to a system with everything tied together so that the “inner loops” of the algorithms are implemented using the FPGA fabric and the rest of the system is implemented in software running on the ARM Cortex processor cores.

How well does it work? Well one example: implementing a video encoder such as MPEG that involves motion detection and not retransmitting parts of the picture that are unchanged or merely incrementally moved, can run at full video rate of sixty frames a second which is a speedup of 700 times from just running the algorithm on the ARM processor.

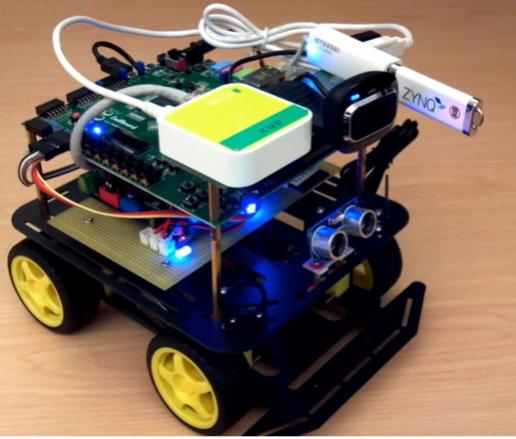

There’s more in the presentation than this. A look at Xilinx’s view of semiconductor technology, educational kits. How about a self driving car? Well, a very small one.

There’s more in the presentation than this. A look at Xilinx’s view of semiconductor technology, educational kits. How about a self driving car? Well, a very small one.

EDPS is in Monterey next Thursday and Friday, April 18th and 19th. The full program is here. Registration is hereand use the promo code SemiWiki-EDPS-JFR to save $50. Call the hotel directly for room reservations.

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center