An engineering change order, or ECO in the context of ASIC design is a way to modify or patch a design after layout without needing to re-implement the design from its starting point. There are many reasons to use an ECO strategy. Some examples include correcting errors that are found in post-synthesis verification, optimizing performance based on detailed parasitic effects and efficiently responding to design enhancements. For the case of mixed signal ASIC design, the challenges become even greater due to the subtle interactions between the analog and digital circuits.

I recently had a chance to preview the content of a webinar to be presented by Easylogic in collaboration with SemiWiki that dug into these issues in significant detail. In under 30 minutes, I was treated to an excellent overview of what challenges exist and how to address those challenges with a well-defined strategy and flow. I learned a lot, and I believe you will, too. Watch the replay HERE. More on that in a moment but first let me give you a few observations about addressing functional ECOs for mixed-signal ASICs.

The Webinar Presenter

The webinar is presented by Richard Chang. Richard brings over 30 years of experience in the VLSI industry to the webinar. He has held a variety of design and management positions that include comprehensive expertise across the entire ASIC/SoC design cycle—from specification, design, simulation, and FPGA prototyping to tape-out and silicon bring-up.

Richard has a relaxed presentation style that is easy to follow. The topic of ECO strategies for mixed signal ASICs can become quite complex, but Richard is able to keep the discussion at the right level to convey key points without getting bogged down in details. The entire webinar content is under 30 minutes. You will take away some valuable information from Richard’s presentation. Let’s look at a few of the topics he will cover.

Key Topics

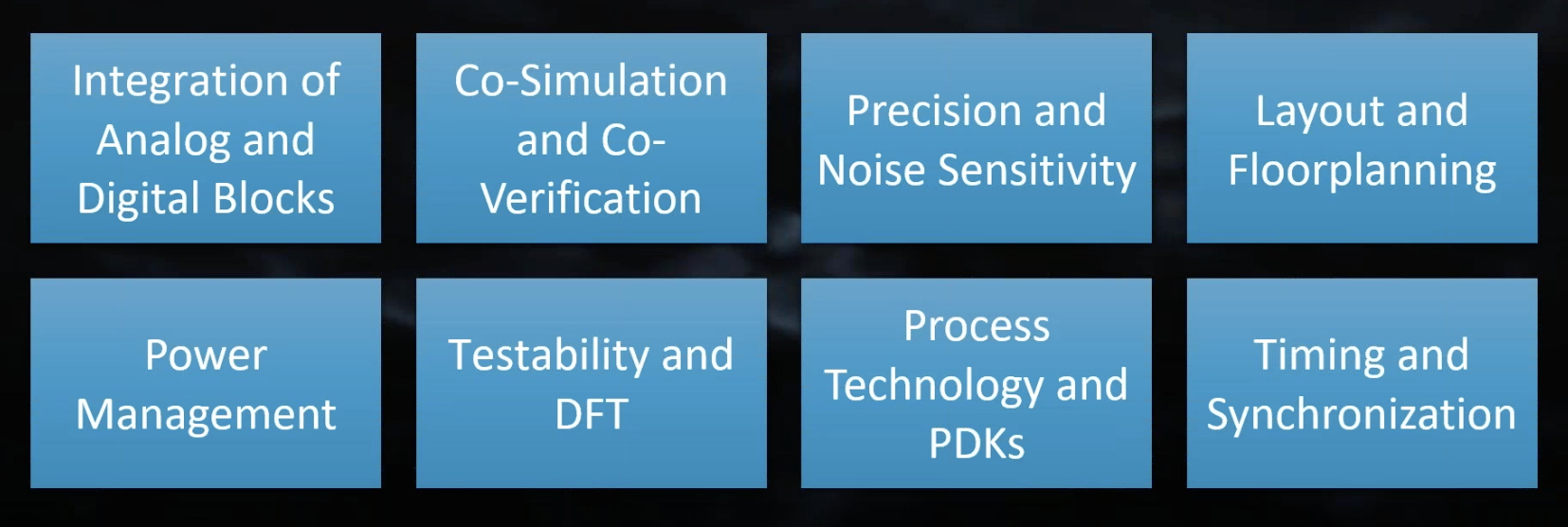

Richard will begin with an overview of the mixed-signal ASIC applications – the broad scope of use for this technology and some of the unique challenges designers face. The diagram below summarizes some of the challenges that he will explore.

Richard also reviews the various events that drive the need for ECOs in mixed signal design. There are three broad categories here:

- What drives manual ECOs at the netlist level

- What types of changes result in frequent ECO requests

- The impact of ECOs on DFT and layout

Richard will provide a lot of detail about all three of these areas with examples. This sets the stage for the portion of the webinar that explains how to manage ECO challenges with Easylogic’s fully automated and patented ECO solution.

Richard will provide excellent detail here to explain how Easylogic fits into the flow and what the resulting benefits are. His discussion will focus on four major themes:

- RTL-based automatic netlist tracing

- Achieving substantially smaller patches

- Shortening the ECO turnaround time

- Seamless design flow integration

He will provide plenty of detail on all these topics, including real design results. Richard will conclude his discussion by pointing out there are hundreds of tapeout successes using Easylogic’s tools.

To Learn More

If ECOs are becoming a larger part of your design flow, you will want to take advantage of the advice provided in this webinar. You can learn more about Easylogic on SemiWiki here, or the company’s website here. And you can watch the replay here. And that’s how you can learn about addressing functional ECOs for mixed-signal ASICs.

Also Read:

WEBINAR: Functional ECO Solution for Mixed-Signal ASIC Design

Easylogic at the 2025 Design Automation Conference #62DAC

Easy-Logic and Functional ECOs at #61DAC

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.