The explosive growth of large language models (LLMs) has created substantial new requirements for chip-to-chip interconnects. These very large models are trained in high-performance data centers. Multiple accelerators need to work seamlessly to make all this possible as the bandwidth between accelerators directly impacts the size of trainable LLMs. It is accurate to say that this new era of AI is driven by new levels of bandwidth and low latency. A critical enabler for all this is 224G PHY technology. But working IP isn’t enough. The IP needs to be interoperable with other parts of the system. Synopsys has held a strong position here, both in terms of high-quality IP and proven interoperability. Let’s take a closer look at the road to innovation with Synopsys 224G PHY IP.

What it Takes to Enable Innovation

I have first-hand experience regarding what it takes to enable innovation through my work at eSilicon. As a fabless ASIC provider, enabling IP and how to design with it was a significant differentiator. We did a lot of work on 56G PHYs, the state-of-the-art at the time. Getting the IP to work across voltage and temperature was only the beginning, however. How the IP interacted with other parts of the system was also a critical care-about for our customers. This included all forms of processing, storage and communication channels. Proving interoperability was no easy task.

It turns out Synopsys has been at this for a while with great results. The company’s 56G IP has been proven in multiple designs down to 12nm. Its 112G IP has been proven in even more designs between 7nm and 3nm. And over the last three years, its 224G PHY has been put to the test.

In September 2022, Synopsys showcased the world’s first 224G SerDes IP demonstration with an ecosystem partner at ECOC 2022 in Basel, Switzerland. This milestone marked the birth of tangible 224G PHY IP. Since then, significant progress has been made with partner demonstrations at shows such as DesignCon, the Optical Fiber Communication Conference (OFC), ECOC, and the TSMC Technology Symposium. Synopsys IP has become the industry’s most widely interoperable 224G SerDes, supporting VSR, LR, and optical channels.

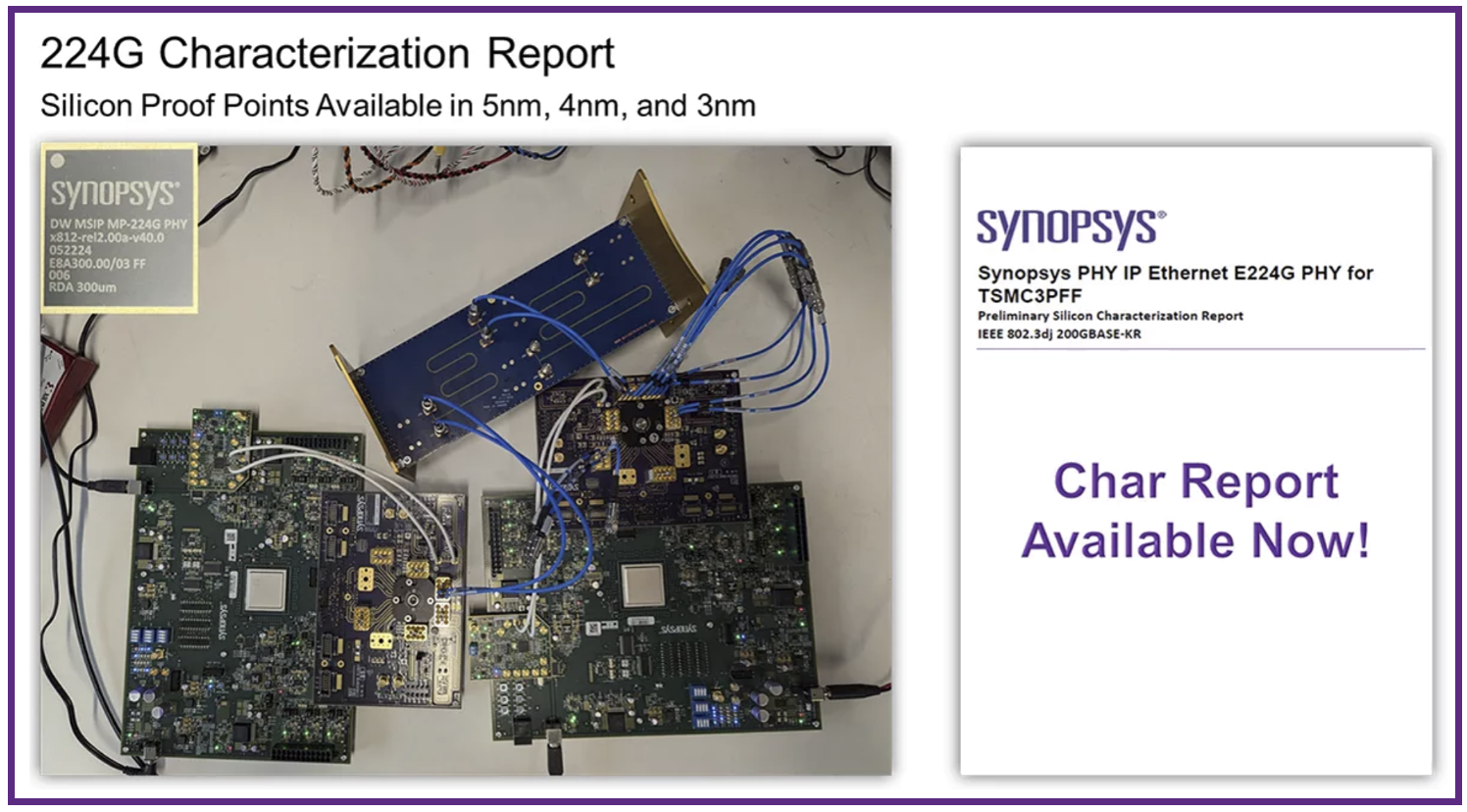

As shown in the graphic at the top of this post, the characterization report for the Synopsys 224G PHY on TSMC’s 3nm process is now available.

Digging Deeper

There are very useful resources available to understand more about the progress that Synopsys has made and the implications of the work. There is a great interactive video entitled How Synopsys 224G IP is Enabling the Future of 1.6T Networking and UALink 200G. In this video. Magaly Sandoval, product & solutions program manager at Synopsys poses some probing questions to Priyank Shukla, product director for Ethernet and UAL IP Portfolio at Synopsys.

Magaly begins with an overview of the market forces at play that have driven speeds to 224G. With that background, she asks Priyank what has the Synopsys experience been with the design and deployment of high-speed Ethernet as speeds have moved from 56G to 112G to 224G ? Priyank goes into significant detail regarding the challenges faced, the varied types of designs being developed and the milestones achieved along the way.

Magaly then summarizes the significant milestones achieved on designs at advanced nodes and she asks Priyank to comment on when these designs will be taped out. Priyank goes into the details about the status of several 224G designs in 3nm and 2nm. Magaly then ends by asking Priyank about standards. What is the completeness of these standards?

There is also a technical article available that is written by Magaly entitled Leading the Charge in High-Bandwidth Interconnects with 224G PHY IP. This report provides substantial detail on the interoperability work Synopsys has been doing with its 224G PHY IP. The details of many designs from 16nm down to 3nm is provided. There is also an embedded video that takes you on a tour of DesignCon 2025 where partners showcase their products working with Synopsys 224G PHY IP. The video includes detailed overviews of the demos presented at the Keysight booth, the Samtec booth, Yamaichi and the Foxconn Interconnect Technology booth.

To Learn More

If you are working to solve interconnect challenges posed by advanced AI, you will need to master 224G channel speeds and proven interoperable Synopsys IP is an important ingredient for success. You can watch the interactive video with Magaly Sandoval and Priyank Shukla here. And you can access the informative technical article written by Magaly Sandoval here. And that’s what the road to innovation with Synopsys 224G PHY IP looks like.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.