Founded in 2016 and based in Barcelona, Spain, Semidynamics™ is the only provider of fully customizable RISC-V processor IP. The company delivers high bandwidth, high performance cores with vector units and tensor units targeted at machine learning and AI applications. There were some recent announcements from Semidynamics leading up to the RISC-V Summit that extend the company’s focus on customization. I had a chance to meet with the company’s CEO at the Summit to get the back-story on what the announcement really means. Read on to get the whole story about how Semidynamics founder and CEO, Roger Espasa, introduces extreme customization.

Founded in 2016 and based in Barcelona, Spain, Semidynamics™ is the only provider of fully customizable RISC-V processor IP. The company delivers high bandwidth, high performance cores with vector units and tensor units targeted at machine learning and AI applications. There were some recent announcements from Semidynamics leading up to the RISC-V Summit that extend the company’s focus on customization. I had a chance to meet with the company’s CEO at the Summit to get the back-story on what the announcement really means. Read on to get the whole story about how Semidynamics founder and CEO, Roger Espasa, introduces extreme customization.

What Was Announced

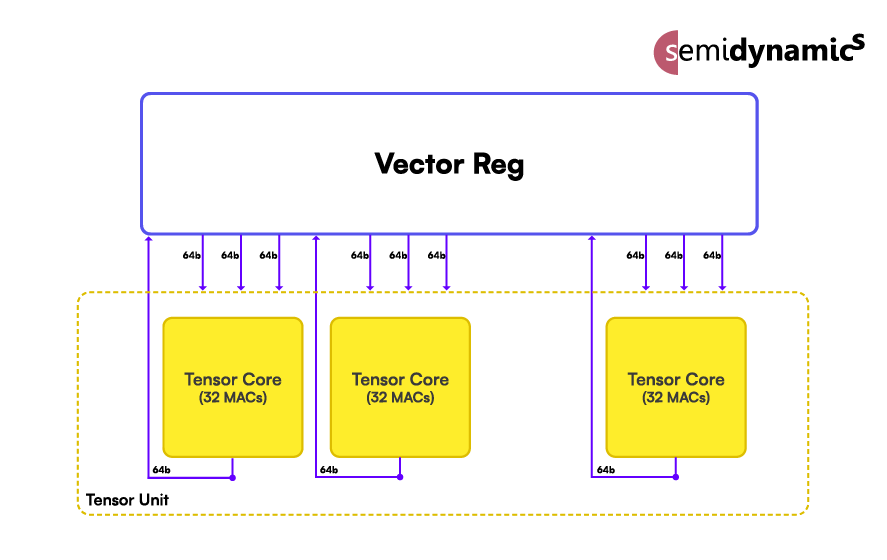

First, let’s look at what was announced leading up to the RISC-V Summit. The headline was Semidynamics launches first fully-coherent RISC-V Tensor unit to supercharge AI applications. The announcement introduced a RISC-V Tensor Unit designed for ultra-fast AI solutions. The design is based on the company’s fully customizable 64-bit cores. The Tensor Unit is built on top of the Semidynamics RVV1.0 Vector Processing Unit and leverages the existing vector registers to store matrices, as outlined in the figure below.

This enables the Tensor Unit to be used for layers that require matrix multiply capabilities, such as Fully Connected and Convolution, and use the Vector Unit for the activation function layers (ReLU, Sigmoid, Softmax, etc.), which is a big improvement over stand-alone NPUs that usually have trouble dealing with activation layers.

The Tensor Unit leverages both the Vector Unit capabilities as well as the Atrevido-423 Gazzillion™ capabilities to fetch the data it needs from memory. Semidynamics Gazzillion technology allows the processor to send up to 128 requests to the memory system, whereas other cores can only tolerate very few cache misses. This means that the processor continues doing useful processing while previous misses are served. It is interesting to note that Tensor Units consume data at an extremely high rate and, without Gazzillion, a normal core couldn’t keep up with the Tensor Unit’s demands. Other solutions rely on difficult-to-program DMAs to solve this problem. Semidynamics took a different approach by seamlessly integrating the Tensor Unit into its cache-coherent subsystem. This innovation effectively opens a new era of programming simplicity for AI software.

The Motivation and Back-Story for the Announcement

I spent some time with Semidynamics Founder and CEO Roger Espasa at the Summit. Dr. Espasa is not your typical high-tech startup CEO. He has been teaching at the Universitat Politècnica de Catalunya in Barcelona for over 31 years. This work has brought him close to a rich pallet of innovation and an array of venture funding sources. Before founding Semidynamics over seven years ago, he was chief architect at Esperanto Technologies, technical director at Broadcom, a principal engineer and silicon architect at Intel, and an architect at Compaq. Roger has done the job of many of his customers. This gives him a unique ability to understand what they need, and his substantial exposure to innovation allows him to see the path forward with a unique level of insight. He explained that he can dig into the challenges of Semidynamics customers and help to develop unique, focused and highly efficient solutions. And this focus on problem-solving and making its customers successful is what created the new architecture that was announced and demonstrated at the show.

As Roger explained, customers told him they loved the Vector Unit architecture Semidynamics provided, but, for challenging AI workloads there was always a need for more. That request “for more power” is what led Roger and his team to add the Tensor Unit to help address the need for vast processing power. Roger pointed out this enhancement was delivered as part of the RISC-V ISA, making it easier to integrate the Vector Unit, Gazzillion technology and now the Tensor Unit into AI workloads. Ease of programming was a key feature, and Roger’s years of system design experience helped to drive that delivery. He explained that his customers are making huge investments in the SoC that will bring their new product idea to life. Their company is on the line, and Semidynamics intends to remove as many barriers as possible to enable success. This attitude means embracing special requirements, and that’s how Semidynamics founder and CEO Roger Espasa introduces extreme customization.

Also Read:

Deeper RISC-V pipeline plows through vector-scalar loops

RISC-V 64 bit IP for High Performance

Configurable RISC-V core sidesteps cache misses with 128 fetches

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.