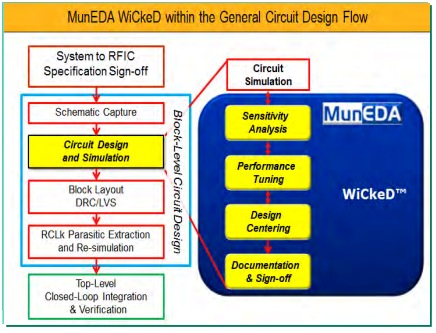

On Wednesday at DAC I met with Bob Slee, distributor and Michael Siu, AE for MunEDA to get an update on what’s new. MunEDA has EDA software for:

- Schematic porting

- Nominal circuit analysis

- Nominal circuit optimization

- Statistical circuit analysis

- Statistical circuit optimization

- IP porting

- Circuit model generation

More important than just EDA tools they have tier one semiconductor customers using these tools.

Users: AMS designer, IP design, custom, memory – use Wicked to help optimize a netlist. User will define which transistors to change or vary, then tool will invoke SPICE circuit simulator, measure results. Specify: W, L, VDD or even process parameters.

Example: OpAmp circuit with a required gain. Wicked will optimize to try and reach the goal. If it cannot reach that spec it tells you.

WICkeD works with: Spectre, HSIM, Eldo, etc. simulator indepedent.

WICked: About 10 years old. From Technical University of Munich, help from Infineon.

Customers: Samsung, Toshiba, Hynix, ST, Infineon, ON Semi, ST, Altera, Faraday, Bosch, Atmel, IR, Fraunhofer, X Fab, Dialog Semi.

Sales: Contact your representative.

Time based license.

WiCkeD – Worst Case Distance for optimization.

Share this post via:

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era