Most IC designers I talk to really enjoy the creative process of developing a new SoC design, debugging it, then watching it go into production. They don’t really like spending time learning how to make their EDA tools work together in an optimal IC design flow where they may have a dozen tools each with dozens of options. Fortunately for Synopsys tool users there is now a short-cut offered in the form of the Lynx Design System, which has already captured the digital design flow so you can focus on design instead of CAD integration.

On Monday I spoke by phone with Will Robbins of Picochip (now being acquired by Mindspeed Technologies Inc.) and Matt Gutierrez of Synopsys about how Lynx is actually being used in a 40nm production tool flow.

Will Robbins, Picochip

VP of Silicon, Tools and Platforms

Matt Gutierrez, Synopsys

Director of Marketing, Professional Services & Solutions Group

Q&A

Q: What is Lynx all about?

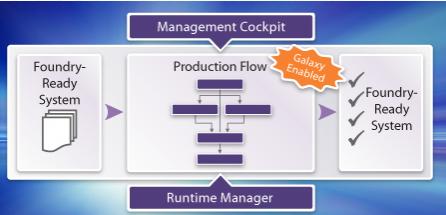

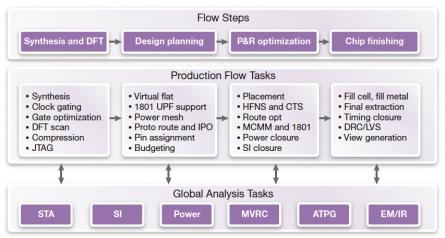

A: Matt – Lynx is kind of unique, because it’s a complete RTL to GDSII design environment for Synopsys digital implementation tools including Design Compiler for logic synthesis, IC Compiler – P&R, Prime Time – Static Timing, Star RCXT – extraction. You can get the source code and integrate any third party tool (like Calibre for DRC/LVS). Lynx does also interface with Custom Designer, seamlessly exchanging data for a unified digital and custom design flow.

Q: What happens as I add my own 3rd party tools into Lynx?

A: Matt – Lynx readily accommodates 3[SUP]rd[/SUP] party tools, though the value in having a proven, pre-test flow decreases if you replace the core tools: Synthesis, P&R, STA, Extraction.

Q: Why did Picochip start using Lynx?

A: Will – We were trying to get our newest IP into silicon quickly. We need all the tool configurations setup for success without a high learning curve. The point is that the tool details are already pre-configured for working. This is really leveraging the experience gained at Synopsys using their own tools in the professional services group, and therefore makes less emphasis on our CAD efforts. We have IC designers that do some CAD work, however there are no real full-time CAD engineers needed when using Lynx. Why should we spend time configuring Design Compiler when it’s all set to go with Lynx?

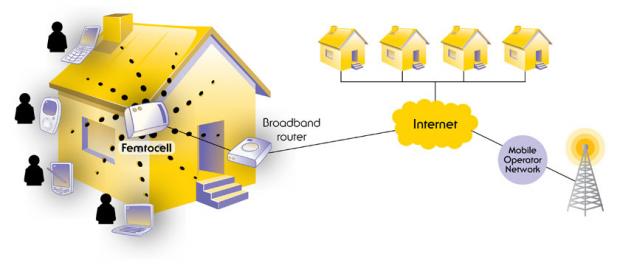

PC3008, 8 user, residential, femtocell using HSPA+

Q: What was your test approach and how about DRC/LVS tools?

A: Will – We use DFTMAX to insert scan into blocks. The design is very hierarchical so we connect up the chains manually at the top level of the device, which then allow us to test replicated blocks in parallel, so saving test time. The scan chains use compression – again to save test time. We successfully ran Synopsys Hercules tools for LVS/DRC on the TSMC 40nm process.

Q: Where do customers share their ideas on customizing Lynx?

A: Matt – They can use Solvnet and share their scripts, and read application notes that we’ve created.

Q: How does a foundry work with Synopsys to validate the flow used by Lynx?

A: Matt – Foundries collaborate with Synopsys to make Synopsys tools and flows work for the newest nodes and libraries. Lynx can work with any foundry and library, so we support the major foundries and nodes out there today.

Many foundries offer a reference flow. Lynx extends that idea into a full and tested production flow with Synopsys tools.

Lynx helps IC design teams to accelerate their projects by leveraging our experience with tools and chip design. Our best practices are built-in to the Lynx flow, so they don’t need to invest their own time to develop a tool flow.

Q: What happens when tools upgrade?

A: Matt – Since Lynx’s flow is tcl script based, new tools can be incorporated at any time in the project. A new version of Lynx is not required when a tool upgrades. However, most design teams freeze their tools and versions at the start of their project.

Will – I see Lynx as a validated set of tools, not discrete tools, so we take the validated set specified in a Lynx release from Synopsys rather than tracking particular tool releases. That said we do update some tools to fix specific issues.

Q: How large is the professional services group at Synopsys?

A: Matt – In Design Consulting Synopsys has 200 people in services.

Q: Does Picochip hire Synospsys for services?

A: Will – Yes, at Picochip we hired one professional service engineer from Synopsys on our recent project, and he helped from start to finish. The service engineer was remote and also in our office. We’ve had a relationship of over 8 years using professional services from Synopsys.

Q: Tell me more about the Synopsys service group.

A: Matt – At Synopsys we are an early adopter of our own tools, providing feedback to development about the tools as we use them daily in our design work.

Q: How would your design consultant access your tools and work?

A: Will – For remote access we use VNC over VPN as a remote desktop.

Q: What if I wanted my design and tools to be hosted by Synopsys?

A: Matt – Synopsys has something called Design Sphere where the flow and database can reside at Synopsys servers.

Q: How did first Silicon turn out on the PC3008 design?

A: Will – Very well, we are sampling PC3008 to customers now. Picochip is currently being acquired by Mindspeed (also a Synopsys customer). The PC3008 as an HSPA product will form a very strong portfolio with the Mindspeed’s LTE small cell products.

Q: What is a Femtocell?

A: Will – A femtocell is small cellular base station. It is used in home or office enviroments. It routes the data through your home broadband. It provides both improved in building coverage and addition network capacity. The latter is vital as mobile data volumes continue to soar. The PC3008’s small footprint and low power enables the building of a USB Femtocell.

Q: How complex is the PC3008 chip design?

A: Will – The PC3008 is a full residential Femtocell SoC. It integrates the full HSPA and PHY – with ethernet MII at one end and radio interface on the other; it is a base station on a chip. The stack is run on a 1GHz ARM11. It integrates several advanced security systems to secure the traffic in and out of the femtocell and the femtocell itself. From this you can see the device is comples. It is compose of 150Million transistor. We make use of a significant of Synopsys Verification IP in the design process.

Q: What about prototyping your SoC?

A: Will – Not yet, we just use more Linux boxes and run more VCS. We are designing with Verilog for RTL, and SystemVerilog for test-benches. Matlab is also used for architectural exploration (DSP), then we can verify versus RTL using VCS and Formality.

Q: How much does Lynx cost?

A: Matt – Lynx pricing is not disclosed, its licensed separately from the tools, and is attractively priced. The source code is sold as a perpetual license, and you can buy maintenance annually.

Q: What about updates for Lynx?

A: Matt – Our Lynx releases keep paces with tool releases, and we have Service Pack releases multiple times throughout the year. Large releases occur about every 9 months. We support Linux and Unix systems, Sun OS.

Summary

Picochip has used the Lynx Design System to bring up a working IC design flow on their 40nm project in just 2 weeks, which was only 20% the time required on previous flows. In addition Picochip hired a Synopsys engineer on this SoC project. The goal of Lynx is to optimize an all-Synopsys digital tool flow, so I can see some room for other consulting groups and EDA companies to extend the Lynx Design System to integrate more 3rd party tools.

Comments

0 Replies to “How Is Your IC Design Flow Glued Together?”

You must register or log in to view/post comments.