The automotive segment is moving from a kind of niche, filled with commodities and highly specialized low complexity IC, to an innovative and very dynamic segment attracting most of the big players, from Qualcomm to Nvidia or Intel. These chip makers are targeting automotive as they need to find new growth areas, and they have quickly adapted their application processor offer from mobile to automotive, more specifically to ADAS and autonomous vehicle.

But this automotive segment is completely different from the consumer segment, as most of the applications are safety critical. That’s why you need to understand standards like ISO 26262 or ASIL. To target applications like ADAS, radar, or safety-critical sensors, even if you market a CPU IP and not and IC, you need to have invested well in advance to propose an ASIL D compliant core…

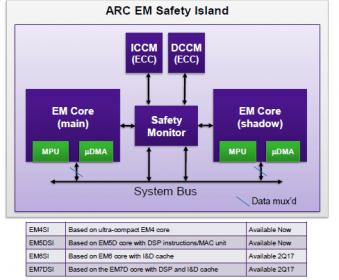

Synopsys has made this investment several years ago for the ARC EM CPU IP family, targeting the most challenging automotive specification, the ISO 26262 ASIL D. Meeting this specification means that you must have less than 1% single point of failure in the entire system. For processors going into ASIL D certifiable chips, this translates into several stringent requirements, like:

·Caches and tightly coupled memories need error correction and detection

·Implement a redundant (or shadow core) running same code

·Insert logic to monitor and compare results from redundant cores

·Build extensive safety documentation for ISO 26262

The next picture describes the implementation of pre-built ARC EM Safety Islands, verified and ASIL D Ready certified dual-core lockstep processors with integrated safety monitors. Interesting to notice, ARC EM cores with Safety Enhancement Package are the only processors in microcontroller class with ECC on memories and lockstep interface…

In fact, if the application processor chip makers are targeting master processing for ADAS or even autonomous vehicle application, there will be plenty chips around this master to support sub-systems like Radar, Lidar or sensor fusion. But these sub-systems will also be part of the safety-critical system and they will need to comply withISO 26262 ASIL D specification. In this case, the chip maker will select the Lock Step implementation.

If a customer is targeting an automotive application, but not safety critical, he may use the ARC EM IP core complying with the least stringent ASIL B specification and implement the Independent Dual Core mode.

To reduce single points of failure, Synopsys has implemented tightly coupled interrupt controller and options such as MPU andmDMA to provide full redundancy.A CPU IP core is not just made of dedicated hardware, and the compiler is part of the IP vendor offer as it’s an essential piece supporting the project development. The fact that the MetaWare compiler is alsoASIL D Ready certified will significantly accelerate ISO 26262 compliant code development.

The border between a microprocessor and a DSP is becoming blurry and the EM5D cores inside the EM5DSI support various DSP features like fixed point DSP, vector and single instruction/multiple data (SIMD) processing. They include a unified, single-cycle 32 x 32 MUL/MAC unit with 32-bit/64-bit accumulators. To deliver enhanced performance for filtering, FFT and other signal processing algorithms, the EM5D also features fractional support, rounding and non-rounding instructions, as well as divide, square root and fixed-point math functions. Vector and SIMD support provide greater processor efficiency by enabling multiple data values to be processed in a single operation.

The best way to describe an IP may not be to list a set of features, but rather to look at the type of applications which can be supported by this IP. For example, the EM5DSI can be used to process Vision ADAS, Radar and Smart Sensors, and each of these applications can potentially be on the safety critical path.

Vision processing is needed to help driver assistance and autonomous driving and the requirements are expected to move from ASIL B to ASIL D for the hardware supporting such safety critical application. This transition should be simplified when using the ARC EM Safety Islands, positively impacting the TTM.

The ARC EM Safety Islands can provide front end processing for Radar application. If the Radar technology is used for driver assistance and autonomous driving, the ASIL D requirements will be met faster when implementing such ASIL D ready certified solution, including the compiler.

Because many sensors are in the safety critical path for applications like braking or steering, the CPU core handling processing for smart sensors and controllers has to comply with the ISO 26262 ASIL D firm requirement. Selecting a certified IP solution will guarantee the compliance and will shorten the TTM.

By Eric Esteve from IPnest

The ARC EM4SI and EM5DSI Safety Islands and the MetaWare Development Toolkit for Safety are available now. The ARC EM6SI and EM7DSI Safety Islands will be available in Q2, 2017.

More about DesignWare ARC Processor Solutions for Automotive Applications:

·ARC EM Safety Island IP

·Safety Option for ARC EM Processors

Comments

0 Replies to “Driver Assistance and Autonomous? Need ASIL D Ready Certified CPU!”

You must register or log in to view/post comments.