A few weeks ago we previewed a Synopsys webinar describing how they are linking the ARM Juno Development Platform with the HAPS-80 and HAPS ProtoCompiler environment. I’ve had a look at the archived event and have some additional thoughts.

We introduced the ARM Juno SoC and development board and the ARM LogicTile FPGA expansion daughtercard last time (link to that post below). It’s become the defacto reference platform for software development on ARM Cortex-A57 (or Cortex-A72) and Cortex-A53 big.LITTLE clusters. and a newer version with a Cortex-A72 and Cortex-A53 cluster. It also provides a look at a Mali-T624 GPU and the CCI-400 cache coherent interconnect, along with a DDR3 memory subsystem, an optional PCIe controller, and a Cortex-M3 core for system control functions.

Synopsys recognizes that this configuration is widely used in the software community, including those working on Linaro and Android, to develop trusted firmware, boot loaders, and operating systems. What happens if your efforts are more I/O oriented, beyond the features on the base Juno development board, and larger than one LogicTile with a Virtex-7 XC7V2000T can handle? That does sound like for a case for HAPS and FPGA-based prototyping – but, it would be a shame to just toss out the completely ported Juno recreate and recreate all of that in a HAPS platform.

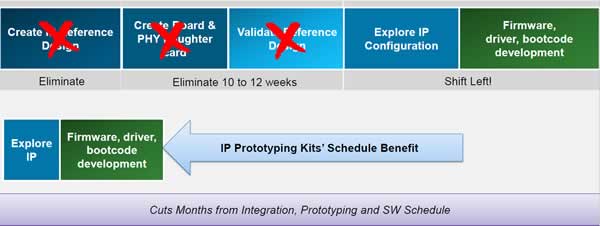

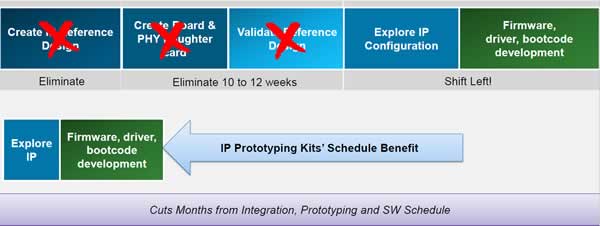

In fact, Synopsys estimates it could be at least 10 to 12 weeks’ worth of shame to do that, and that’s assuming you get the setup right. It is very interesting they toss out that figure; we’ve had plenty of discussions on how flexible FPGA-based prototyping is, but one of the drawbacks is there is some setup time. In this case, creating the big.LITTLE cluster with GPU and cache coherent IP (assuming you have all that licensed), getting the OS of choice running, and adding all the I/O is a big deal when all you really want to do is explore software for a particular piece of IP added to the ARMv8 environment.

What if there were a pre-verified ARMv8 reference design ready for hardware and software IP to be added with much lower risk? Synopsys has simply taken the LogicTile concept and created their own daughtercard to link the Juno development board to the HAPS-80 or HAPS-DX.

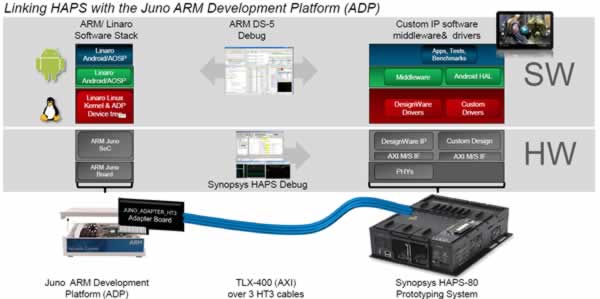

A physical link is created over 3 HapsTrak 3 cables launched from the adapter in the LogicTile socket. Logically, the connections leverage TLX-400 ThinLinks, a low-pin count mechanism to route AXI from the Juno to external hardware. Four groups of I/O provide a configuration bus, a system bus with interrupts and clocking, a ThinLink Master Interface (TMIF) where Juno can master transactions, and a ThinLink Slave Interface (TSIF) for HAPS to master transactions.

Now, the hybrid prototyping solution looks like this:

Admittedly, Synopsys is in the business of selling DesignWare IP, and they deploy this exact hybrid prototyping solution in their labs to verify their IP on ARMv8. For example, Synopsys shows how their DesignWare USB 3.0 IP connects quickly, complete with a testbench, to the Linux Kernel Mainline USB 3.0 Host Driver.

Conceptually, this hybrid prototyping approach works for any IP: there’s an AXI bi-directional interface, and a custom driver and middleware stack lays on top allowing development of software. One could certainly mix and match DesignWare IP or other third-party IP with in-house developed IP.

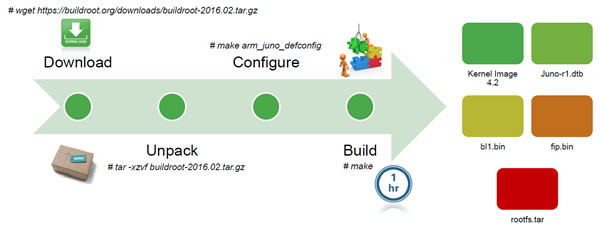

Most importantly, there is absolutely no messing around with the Linaro stack – Synopsys supplies the fip.bin and the bl1.bin, and full Buildroot support ready to go in the Juno/HAPS configuration.

With all that in place, the value proposition of a HAPS-enabled development flow with ProtoCompiler and debug capability kicks in, which we’ve shared many of details on in other posts – the webinar concludes with a short demo video and a quick look at the flow for those less familiar.

Our preview post with some of the Juno background:

Webinar alert – Hybrid prototyping for ARMv8

Registration page for the archived webinar:

Speed Software Development and IP Validation for ARMv8-based SoCs using Juno ARM Development Platform

This focused on the Linaro stack, prebuilt by Synopsys. I can see a lot of utility for this approach in OPNFV, and it would be a matter of creating the necessary firmware image and initialization for the HapsTrak adapter. Synopsys tends to be customer-driven in these efforts; no promises, but I’d expect to see other software stacks down the road as ARMv8 makes inroads on “servers”, or at least some application notes on how a customer could do that.

It does embrace the prime directive of open source, however: don’t recreate the base value, build on top of it. It’s possible smaller projects could get by with only a Juno and a LogicTile, but for larger efforts the HAPS option for hybrid prototyping is a good one.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.