When I upgraded cars from a 1988 to 1998 Acura it seemed like my car had become much smarter with a security chip in the key, security codes in the radio and a connector for computer diagnosis, however in today’s modern auto there’s a lot more mixed-signal design content. Micronasand Synopsysgot together and hosted a webinar two months ago, “Advanced Mixed-Signal Design and Verification of Smartcar ICs“, so I watched it today.

BMW with massive amounts of electronics

Marco Casale-Rossi from Synopsys started out first by comparing the number of 14nm transistors on a 300 mm wafer as being more than the number of stars in the Milky Way galaxy, the infinitely large. The pursuit of every-smaller process nodes is approaching the infinitely small. Car electronics are not designed at the bleeding edge of 16nm because of the long design cycle times, and cost controls. Automotive ICs can span from 1V power supplies up to tens of volts, operate in extreme temperature regions, and often contain mixed-signal IP blocks. An AMS process for automotive may contain: double-poly, triple-well, few metal layers, bipolar, CMOS, DMOS, SRAM, NVM, high voltage and sensors.

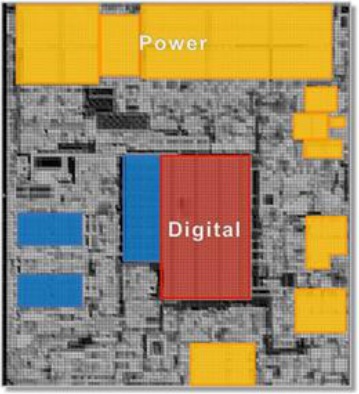

Source: IDM 2013, a 160nm mixed-signal design

Designs can be analog on top, digital on top, or any mixture in-between. EDA tools for automotive should enable lower design and silicon costs. An IDM designed with DC Graphical and IC Compiler to produce an automotive chip in a 110nm process that was 18% smaller in size, with a 13% higher utilization, and a 77% double via rate to improve reliability.

Related: AMD Design IP Deal with Virage Logic. Oops. Synopsys

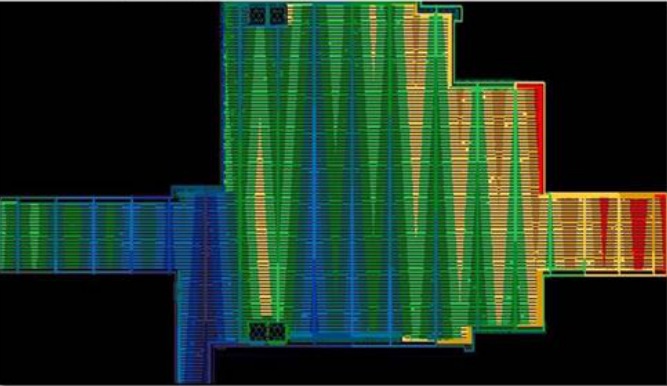

IR drop and electromigration analysis are crucial for predicting the reliability of automotive chips, and an IDM used PrimeRail and IC Compiler for their integrity analysis and resistance calculations.

Source: IDM 2013, a 130nm mixed-signal design

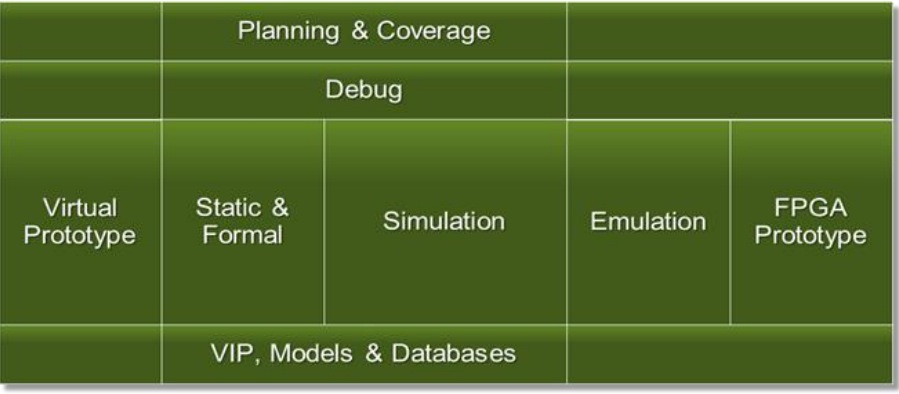

Functional verification from Synopsys spans a wide range of tools, now called Continuum Vision. The technical goal is better and faster verification by finding more bugs, sooner:

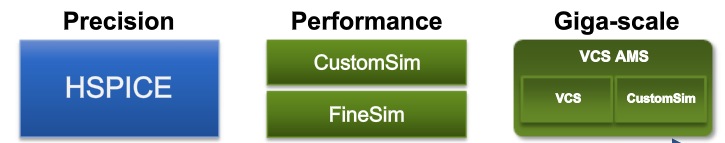

A feature called CircuitCheckis used within the transistor-level, FastSPICE tool CustomSim to help detect bugs during the design phase. Circuit designers have several simulators for use during AMS design, and you choose based upon the required accuracy and capacity:

Mario Anton from Micronas was the second speaker, and his company has 900 people that design, fabricate, test and supply hall sensors and sensor-based products to the automotive industry with a goal of zero ppm quality levels. Micronas started back in 1952, and so far have shipped some 2.5 billion hall sensors. X-FAB also has a fabrication partnership with Micronas.

You’ll find Micronas chips in automotive applications like:

- Powertrain (active pedal, gear position, battery management)

- Chassis and safety (steering torque, chassis height, steering motor position, braking)

- Body and comfort (seat position, window position, wiper position, grill shutter)

Related: Why do you need 9D Sensor Fusion to support 3D orientation?

Outside of automotive, there are Micronas chips for industrial applications like building and home automation, heavy machines and factory automation, plus white goods and home appliances.

Hall-Effect sensors from Micronas are used in automotive as switches, current sensors, angular sensors and linear sensors. Electronic throttle control replaces the mechanical system. Every electric motor in an auto has embedded servo-drives.

For design and verification the engineers need to meet safety requirements defined in ISO26262, and design for zero PPM levels. The IC design flow includes analog full-custom, mixed-signal and digital.

Related: How to Trim Automotive Sensor?

The final speaker was Gernot Koch of Micronas and he shared about their specific design and verification approaches using a range of tools for analog on top:

- Full SPICE

- FastSPICE

- Verilog + SPICE, co-simulation

- Verilog + Verilog A + Verilog AMS + SPICE

- Verilog with Realtype modeling

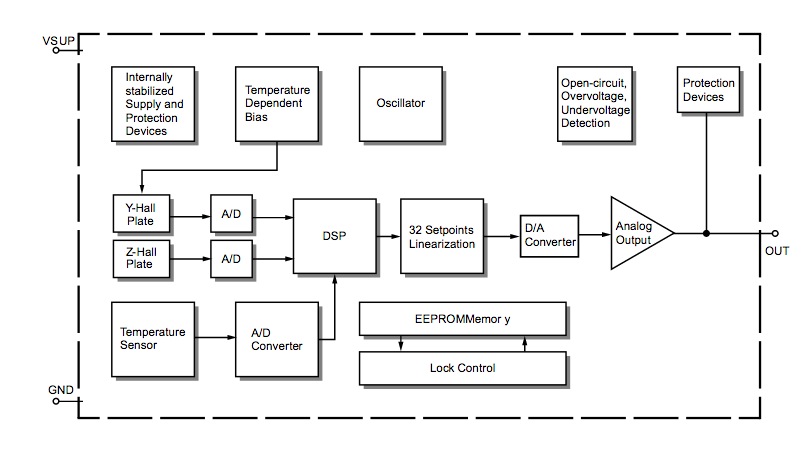

The typical HALL chip architecture is shown below, which includes dozens of different IP blocks:

A small Hall sensor chip with about 5,000 transistors, and a full-custom design approach was taken, using FineSim for circuit simulation. A medium sized Hall sensor with 50,000 transistors had both analog and digital content, so FineSim and VCS simulators were used. On the high-end of hall sensors there were 100K transistors; so HSPICE, FineSim, CustomSim and VCS simulators were part of the design and verification flow.

Simulating with FineSim on multi-cores showed up to a 20X speedup versus an internal SPICE circuit simulator.

The plans at Micronas are to have more teams use the Synopsys tool flow for AMS designs, and replace their internal simulator with FineSim instead because of the speedup provided.

View the entire 52 minute archived webinar here, after a brief registration process.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.