The ARC EM family is the low-power, embedded and low footprint processor part of the larger ARC processor. To target the ultra low-power markets like wearable and IoT, Synopsys has added DSP capabilities to EM5D and EM7D. To be specific, these cores are optimized for ultra low-power control and DSP, thanks to:

- Energy-efficient 3-stage RISC pipeline

- Unified single cycle 32×32 MUL/MAC unit

- Energy-efficient signal processing of voice/speech, audio and sensor data

- Operating Floating Point Unit (FPU)

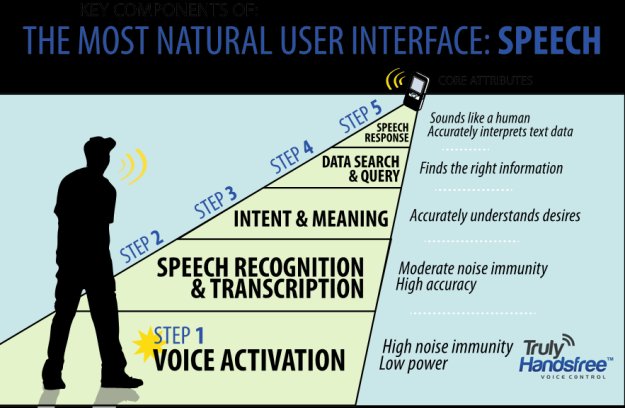

Thus, the EM5D and EM7D cores are especially suited to always-on voice activated and sensor processing applications. The dynamic power consumption of the ARC EM processors can be as low as 3 uW/MHz, particularly well-suited for wearable devices and battery powered applications.

But users are demanding IoT and wearable devices with longer battery life, this is not surprising, and at the same time expect more complex features and better user interface, requiring higher levels of signal processing… and lower power consumption!

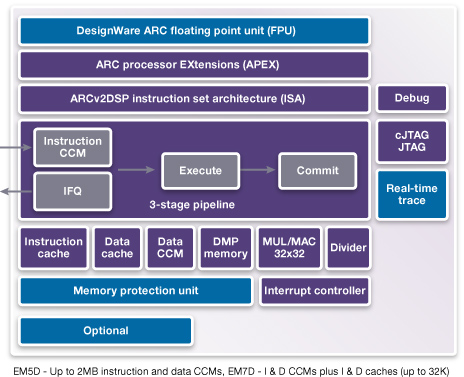

As you can see on the picture below, the ARCv2DSP instruction set architecture (with over 100 DSP instruction) is separated with the parallel 3-stage pipeline, counting 32×32 MUL/MAC unit, square root, divide and butterfly acceleration, as well as various size (2 x 32b/40b or 1 x 64b/72b) accumulators. To cope with customer demand for flexibility, DSP features are configurable, and can be tailored to suit the application. But we have to remember that the power consumption is the most critical feature, thus ARC EM5D and ARC EM7D benefit from enhanced (8 states) sleep modes. Synopsys is claiming 7 uW/MHz power specifications for a core running up to 530 MHz on 40nm LP and delivering 1.77 DMIPS/MHz (or 3.41 CoreMarks per Mhz).

Synopsys propose an evaluation of the power consumption of ARC EM5D (using an RTL simulation including both logic and memory dynamic power) running Sensory’s Power Sound Detection from the TrulyHandsfree Voice control technology and consuming 4 uW, comparing with Competition A (maybe Tensilica?) at 17 uW and Competition B (maybe CEVA?) at 20 uW. Impressive! I can’t guarantee that these data from Synopsys’s competitors are the latest available, neither who is who, even if I am almost sure that A and B are Tensilica and CEVA, or reverse.

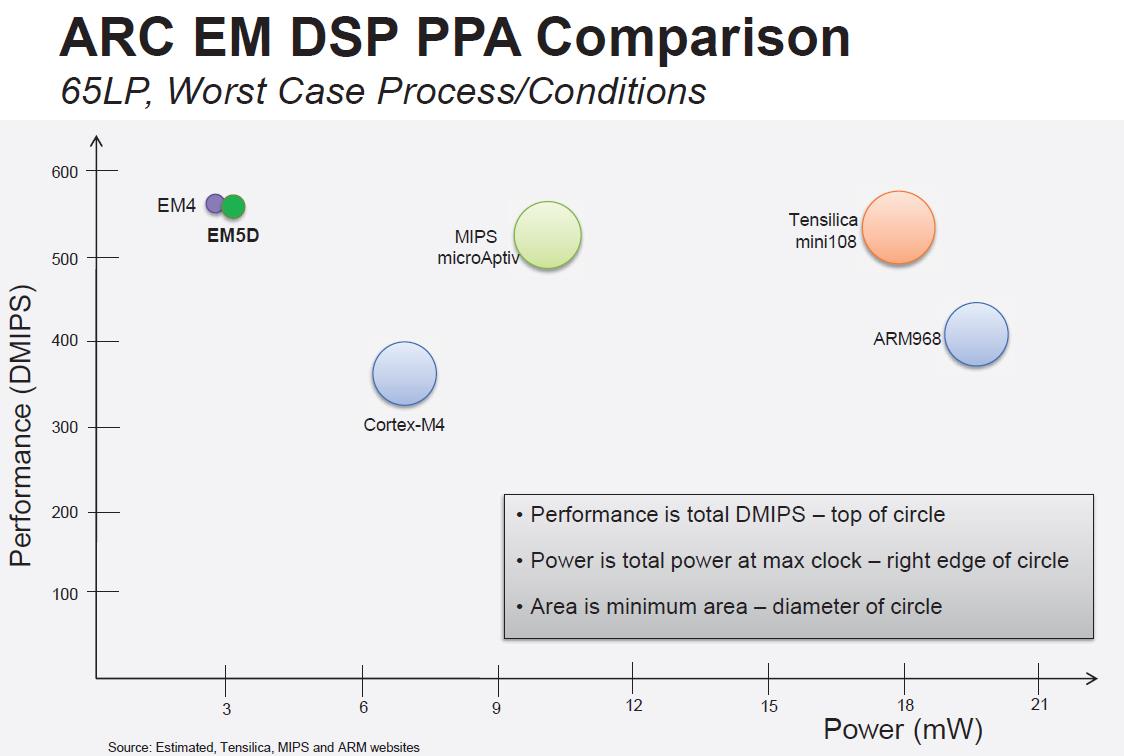

Another interesting benchmark from Synopsys: the Power Performance Area (PPA) comparison of the EM5D (the ARC core with DSP capabilities) with:

- ARM Cortex-M4

- MIPS icroAptiv

- Tensilica mini108

- ARM 968

When interpreting this diagram, you have to remember that you are an engineer, but I think the picture is also accessible to non-engineers. The performance is expressed by the top circle, in total DMIPS, on the Y axis. The power, in mW is the right edge of the circle, on the X axis. And the (Silicon) area is the diameter of the circle. Thanks to the selected competitors, you may compare the circle area (even if there is a geometric amplification, as area is function of the square of the diameter…), as all the competitor’s products exhibit a larger area.

As with any benchmark, the result will depend of the selected competitors, and the selected technology. A larger area on 65LP technology could have a negligible impact on 28nm technology, for example… Nevertheless, these benchmark result qualify the ARC EM DSP enhanced family for addressing IoT and wearable markets, requiring ultra low-power and signal processing capabilities, optimized for signal processing of always-on voice/speech, audio and sensor data applications. The ARC MetaWare toolkit complement this H/W offer, providing rich DSP software library and C/C++ Compiler.

From Eric Esteve from IPNEST

More Articles by Eric Esteve…..

lang: en_US

Share this post via:

Comments

0 Replies to “ARC EM DSP supports Always-on Devices”

You must register or log in to view/post comments.