LSI is an early adopter of Formality Ultra, Synopsys’s tool for improving the entire ECO flow. I already wrote about the basic capability of the tool here. ECOs are changes that come very late in the design cycle, after place and route has already been “nearly” completed. They occur either due to last minute spec changes or the late discovery of functional bugs. The RTL needs to be changed. But if the design has any chance of converging these changes need to be done by hand, finding the nets that need to be updated and then using incremental place and route to fix just those changes without perturbing everything else that already seems to be OK.

LSI is an early adopter of Formality Ultra, Synopsys’s tool for improving the entire ECO flow. I already wrote about the basic capability of the tool here. ECOs are changes that come very late in the design cycle, after place and route has already been “nearly” completed. They occur either due to last minute spec changes or the late discovery of functional bugs. The RTL needs to be changed. But if the design has any chance of converging these changes need to be done by hand, finding the nets that need to be updated and then using incremental place and route to fix just those changes without perturbing everything else that already seems to be OK.

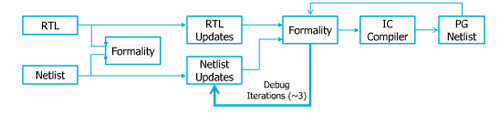

Of course you can’t just go changing the netlist without doing any verification, so historically what would be done would be that a bunch of changes would get batched up and then a full formal verification run would be done to make sure that the new netlist matched the updated RTL and no mistakes had been made. Actually, mistakes often were made and typically around 3 iterations of this loop are required to get closure. Worse, this ECO flow is on the critical path to tapeout.

LSI evaluated Formality Ultra using a reasonably large design: 28nm, 2 million cells, 500K flops, requires 18 hours to run through Formality.

The big challenges with this flow not using Formality Ultra is that:

- finding where to make the changes is time consuming (and ECOs are on the critical path so need to be done fast)

- multiple iterations are required to get the ECOs correct

- netlist updates are required before starting verification

- no matter how small the change, a full Formality run is required

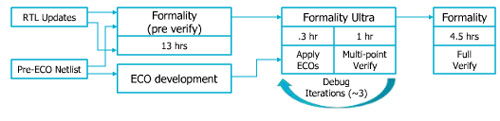

In a Formality Ultra flow, the design is pre-loaded into Formality and then in parallel Formality Ultra is used to develop ECO scripts and apply them. They can then quickly be verified using multi-point (incremental) verification. Any that fail can quickly be debugged, fixed and re-verified. A full verification is done at the end.

The big saving is in time. The pre-verification takes 13 hours on the test design but each ECO and its associated verification takes around 20 minutes for the ECO and under an hour for the verification. Other advantages of the approach are:

- can see the ECO before verification

- find_equivalent_nets reduces errors (50% of ECO errors are the designer misidentifying a net)

- ECO scripts are developed in parallel with verification rather than being batched up

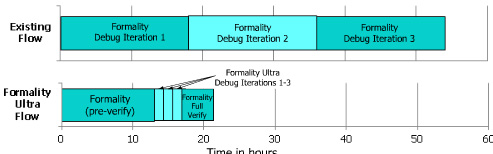

So overall the time is reduced (assuming 3 iterations) from 56 hours down to 22 hours. Perhaps more importantly is that the time for an individual ECO is reduced by a factor of 10 meaning that it is easy to do them one at a time and check each one before moving on, especially trivial fixes like adding an inverter. A large amount of the 22 hours is the fixed time to set up and perform the final verify, not doing the actual ECOs.

There is a webinar presented by Cason Kolb of LSI. It is preceded by a presentation by Mitch Mlinar of Synopsys giving an overview of Formality Ultra. If you already know the basics of Formality Ultra (which I won’t abbreviate to its initials because this is a family blog!) then skip to 21 minutes in.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.