LSI is an early adopter of Formality Ultra, Synopsys’s tool for improving the entire ECO flow. I already wrote about the basic capability of the tool here. ECOs are changes that come very late in the design cycle, after place and route has already been “nearly” completed. They occur either due to last minute spec… Read More

Tag: formality

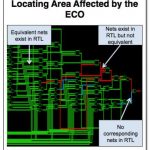

Formality Ultra, Streamline Your ECOs

One of the most challenging stages in an SoC design is achieving timing closure. Actually design closure is perhaps a better term since everything needs to come together such as clock tree, power nets, power budget and so on. Changes made to the design are known as ECOs (which stands for engineering change orders, a term that comes… Read More