Modern SoC (System On Chip) designs contain a larger number of RAM (Random Access Memory) instances, so how do you know what the speed, timing and power are for any instance? There are a couple of approaches:

[LIST=1]

Ken Hsieh of Synopsys authored a White Paper recently about this subject called: The Benefits of Static Timing Analysis Based Memory Characterization. In this blog I’ll cover the second approach, analyzing each memory instance to get the accurate performance numbers quickly.

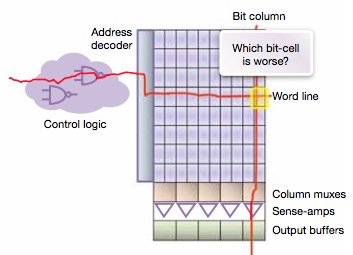

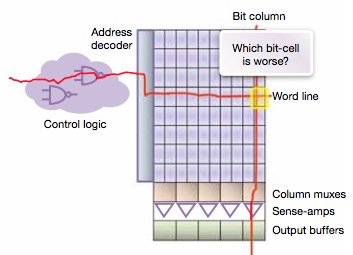

Static Timing Analysis (STA) is applied to the transistor-level netlist of each RAM instance as shown in the following diagram to quickly identify the slowest and fastest paths:

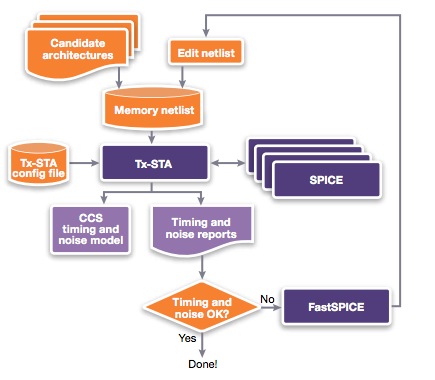

Benefits of the STA approach are that it can quickly find these worst case paths without having to supply input stimulus, or wait for SPICE circuit simulation results. Here’s the design and characterization flow using a transistor-level STA tool, along with SPICE and FastSPICE circuit simulators:

At the top shown in Orange is where a RAM architecture is designed then a memory netlist created. The purple rectangle in the middle denotes the transistor-level STA (Tx-STA) tool that quickly identifies any timing violations per instance and then sends that info to either the SPICE or FastSPICE simulators for further analysis. If the timing and noise results do not meet spec, then the designer goes back to the memory architecture and modifies the netlist. This flow will generate a memory library model called CCS (Composite Current Source) that is within 5% of SPICE results.

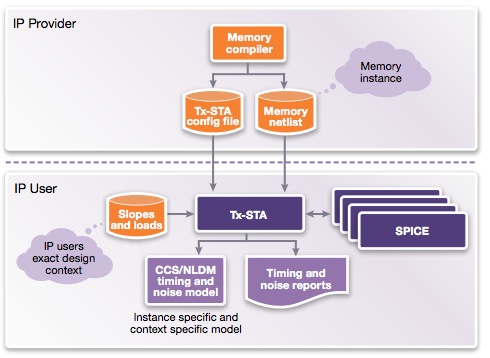

Another flow diagram is shown below after the Memory Compiler has been fully characterized and released into production:

Here the IP provider creates the transistor-level STA config file and netlist. Then, the IP user can quickly run the STA tool on the transistor-level netlist in the context of their entire design (input slopes and output loads). This tool flow is quite fast because the IP user is not required to create input stimulus, or determine what the critical paths are.

The Synopsys tool for Tx-STA is called NanoTime and it has features to perform both setup and hold time checks in an exhaustive manner. Using the CCS models you can get to full-chip SoC signoff.

Summary

Synopsys has an STA-based approach to characterizing and using memory compiler instances that can be quickly and accurately (within 5% of SPICE) completed by both IP providers and IP users. Alternative approaches that really solely upon dynamic circuit simulation require much longer characterization and design times, plus you’re never quite sure that you found all of the worst-case paths.

Further Reading

White Paper: The Benefits of Static Timing Analysis Based Memory Characterization

Comments

0 Replies to “Static Timing Analysis for Memory Characterization”

You must register or log in to view/post comments.