Noise minimization is required for advanced analog and radiofrequency (RF) circuits. Unlike digital circuits, where noise is a second-order effect, system performance metrics such as signal-to-noise ratio (SNR), phase noise, timing jitter, and bit error rate (BER) are directly affected in analog and RF designs. Effective design optimization in the presence of random device noise is challenging because the noise sources are inherent in the circuit elements and cannot be eliminated. Since device noise determines the fundamental limits of circuit functionality, it plays a significant role in analog/RF circuit development.

Noise related issues become particularly critical in circuits with noise-sensitive architectures, tight specifications, and implementation in nanometer CMOS processes with low voltage levels and high frequencies. Most common complex blocks, including analog-to-digital converters (ADC), phase locked loop (PLL), delay locked loop (DLL), transmit chains, receive chains, SerDes, and CMOS image sensors, are highly susceptible to noise.

Measuring and verifying random device noise performance for these circuits can be achieved through a verification hierarchy, starting from smaller building blocks (such as switches, filters) with simple and fast linear noise analysis, to moderate-sized blocks (such as voltage controlled oscillator (VCO), amplifiers, integrators, clocked comparators) using more complex RF noise analysis and sometimes transient noise, and finally, complex blocks (such as ADCs, PLLs, Transmitter, Receiver) using transient noise analysis and in some cases RF noise analysis.

This article will focus on the benefits of full-spectrum transient noise analysis as a must-have for sign-off verification. Full-spectrum transient noise analysis enables engineers to achieve silicon correlation for varied circuit types. It has shown excellent correlation over generations of nanometer process nodes within 1-2 dB of silicon measurements for integer-N PLLs, fractional-N PLLs, and delta-sigma ADCs. In addition, engineers will benefit from the ability to confirm accurate full-spectrum transient noise with proven RF noise analyses (e.g., phase noise of a VCO or input referred noise for a StrongArm Latch).

What is device noise?

Noise in semiconductor circuits is generally divided into deterministic and random sources. Deterministic noise is systematic, bounded, and predictable, while random noise is stochastic, unbounded, and not predictable. Device noise is random and can be categorized into two subtypes: white noise and flicker noise.

White noise

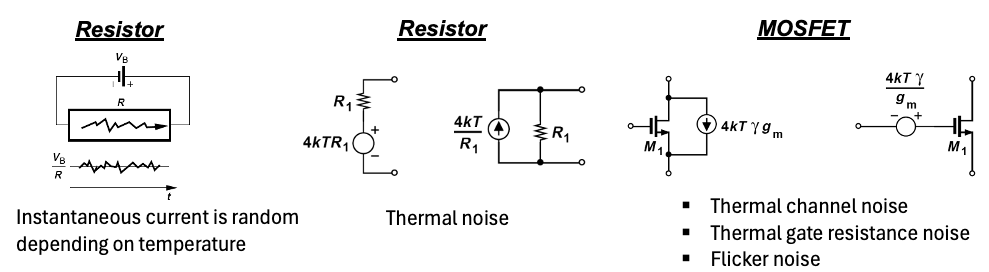

White noise is a random signal with a flat spectral density. The primary sources of white noise are thermal noise and shot noise. The main white noise source in analog/RF CMOS circuits is the MOS device channel thermal noise. Thermal noise results from voltage fluctuations caused by the Brownian motion of electrons in a resistive medium. Thermal noise is found in both passive and active devices. It is broadband white noise that intensifies as temperature increases. Thermal noise has a Gaussian amplitude distribution in the time domain, and its power is evenly distributed across the frequency spectrum. Thermal noise dominates in many applications. Shot noise derives from the discrete quantum nature of electron flow through a potential barrier.

Flicker Noise

Flicker noise, also known as 1/f noise, is caused by traps in semiconductors where carriers that would normally constitute DC current flow are captured for some time and then released. Flicker noise process correlation times are exceptionally long, which makes the power spectral density of flicker noise proportional to 1/f.

What is transient noise analysis?

Transient noise analysis simulates a circuit’s response to random device noise (white and/or flicker). It models transistor noise as current sources with random values based on the noise intensity information from the device model (see Figure 1). Since it is statistical based, the accuracy of transient noise analysis is a function of the number of random samples simulated, i.e., the simulation interval.

What is full-spectrum transient noise analysis?

Full-spectrum transient noise directly solves the stochastic differential equations to generate random noise sources at each time step, uses standard device model parameters for white and flicker noise, changes the noise intensity with instantaneous bias, and shows excellent correlation with other noise methods (linear noise, periodic noise, sampled periodic noise, etc.) on a wide range of circuits (such as VCOs, switched-capacitor circuits, clocked comparators, dividers).

Comparison of transient and transient noise signals

Transient analysis is a ubiquitous verification method for a broad range of circuit types, including digital, memories, analog, image sensors, and RF circuits. It is also utilized for measuring deterministic noise, such as power supply-induced noise. However, transient does not include device noise. To account for device noise, we must run transient noise.

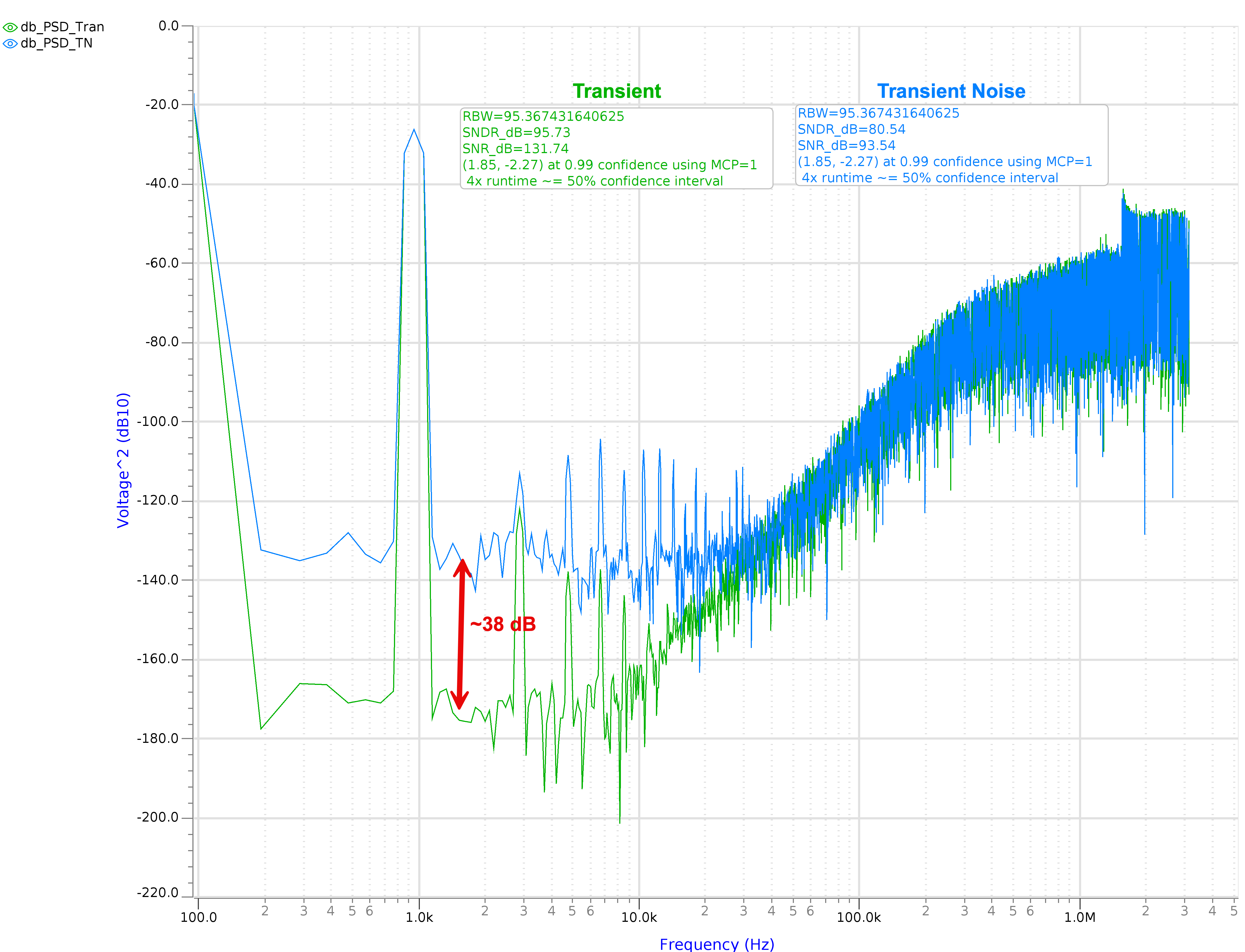

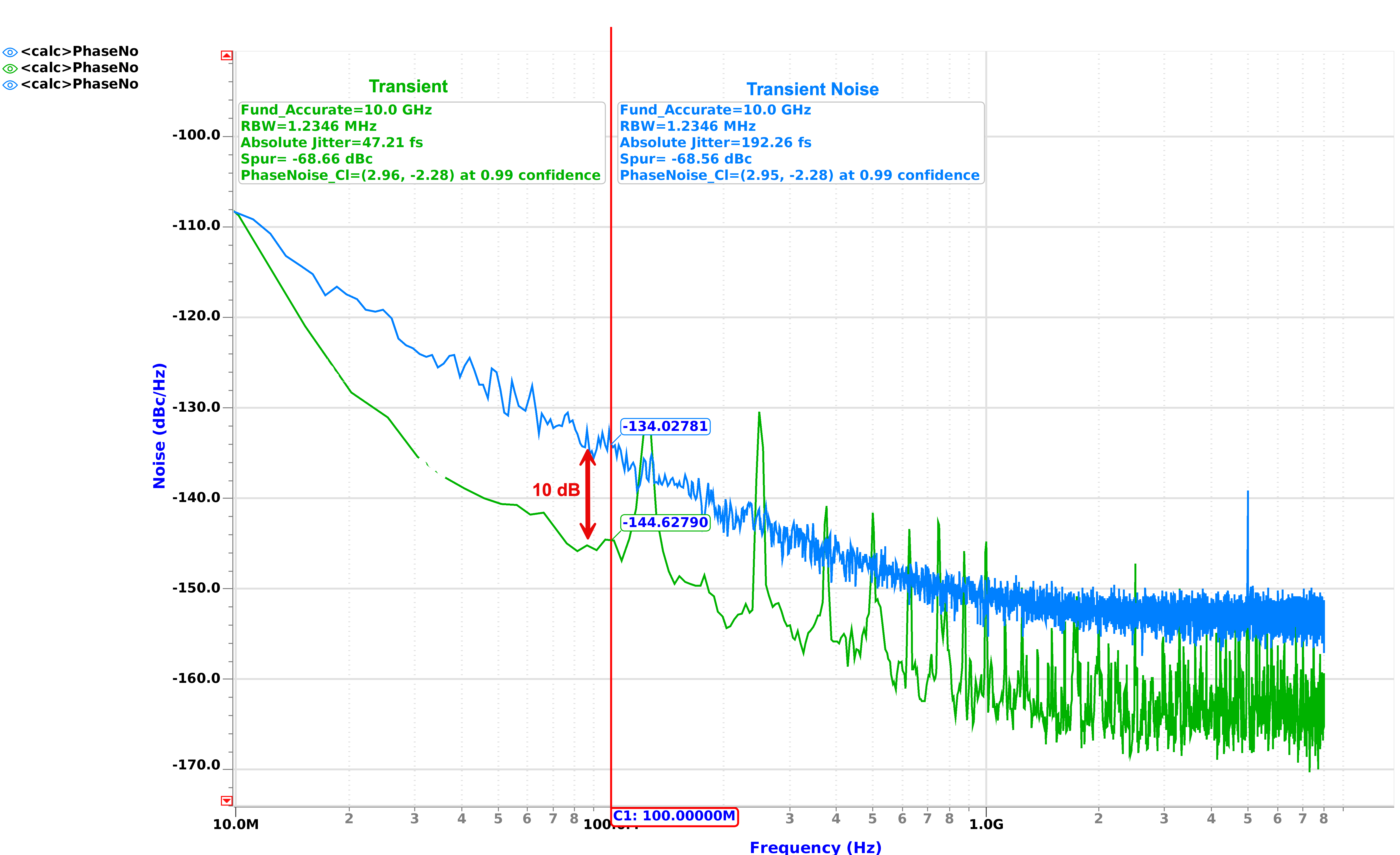

The difference between a transient and a transient noise simulation can be dramatic and significant to a design’s overall performance. Both PLLs and ADCs have metrics to compare noise performance. For ADCs it is signal-to-noise ratio (SNR) and for PLLs it is either Phase Noise or timing jitter. Refer to figures 2 and 3 below to note the drastic difference between transient and transient noise.

The ADC Power Spectral Density (PSD) shown in Figure 2 is a 4th order Delta-sigma ADC measuring the SNR, a common metric for noise performance. There is a ~38 dB difference between the transient and transient noise SNR.

The PLL phase noise shown in in Figure 3 is from an Integer-N Phased Locked Loop (PLL) with the VCO operating at 10 GHz and used in a wireline transceiver. There is a 10 dB difference between the transient and transient noise Phase Noise.

Proper methods to setting up and running transient noise

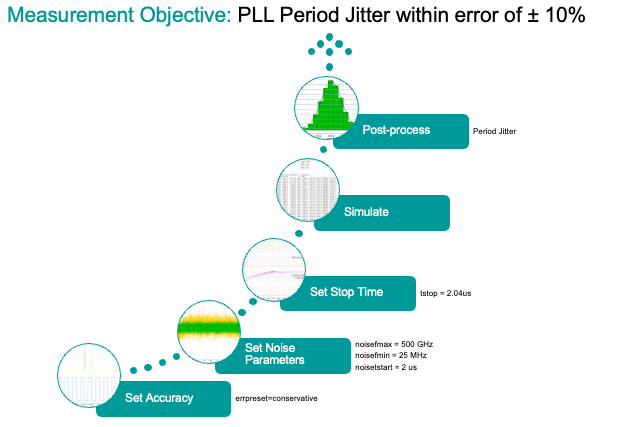

To achieve accurate noise results running transient noise, it is imperative to properly set the SPICE accuracy, noise parameters (noisefmin, noisefmax), stop time, and apply proper post-processing methods. It is not within the scope of this article to go through a detailed explanation of all the parameters, option settings and post-processing steps. The example below (see Figure 4) shows the steps to setup, simulate, and measure PLL Period Jitter to give you a sense of what the process entails.

Why we need to consider confidence intervals when measuring transient noise results

You will notice a label “PhaseNoise_CI” in Figure 3. This stands for the Phase Noise Confidence Interval. The confidence interval measures uncertainty around the phase noise measurement (-139.34 dBc/Hz) at 100 MHz. While running transient noise, we measure a stochastic or random process. Because of this, we cannot simply measure an output such as signal-to-noise ratio (SNR) or phase noise as a single value and report the results, since it does not include the uncertainty of the measurement. As with Monte Carlo simulations, which deal with random process variations, we must also include a confidence interval and confidence level to give us an idea of the uncertainty of the measurement. The confidence interval or uncertainty can be reduced by varying the noise seed in parallel runs.

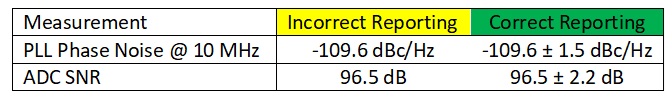

Below is a table showing an incorrect reporting of measurements for a PLL and ADC. Note that the correct reporting includes uncertainty.

Building confidence in your transient noise results

Transient noise is broadly adopted for various circuit blocks, architectures, and process technologies. However, for the unfamiliar, although it may seem a reasonable approach, designers may be uncomfortable or uncertain of its accuracy and methodology. Several whitepapers and presentations show Siemens Analog FastSPICE (AFS) Transient noise correlation to silicon measurements for both PLLs and ADCs over many generations of process nodes, including FinFET process. This is the most convincing approach.

However, as an alternate approach, comparing different and trusted analysis methods (such as linear noise, PNoise, Sampled PNoise, HBNoise) to transient is a viable approach to build confidence in the results.

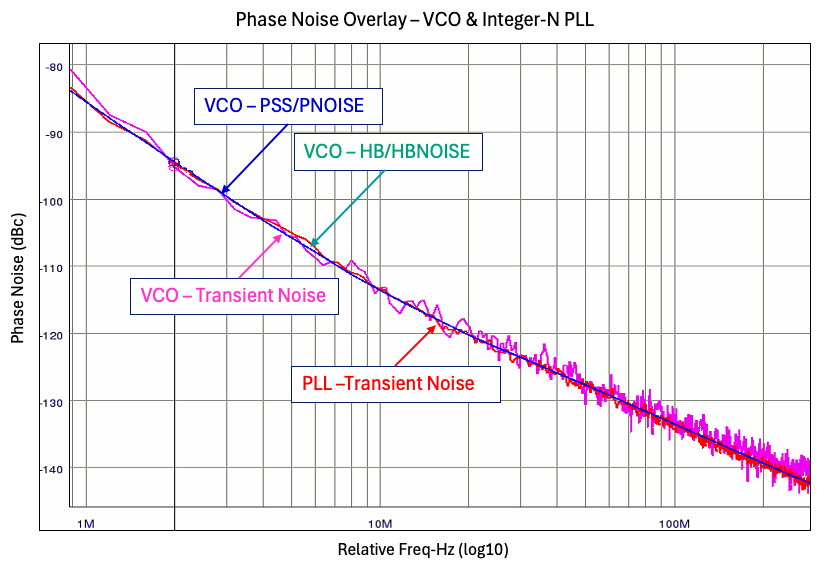

Using a common Integer-N PLL we can compare various analysis methods and see if they match. This is a useful circuit as we know the VCO dominates the phase noise at higher offset frequencies above the PLL bandwidth. Because of this, we can measure the phase noise for the following

- VCO Phase Noise – running PSS large signal and PNoise small signal analysis, HB large signal /HBNOISE small signal analysis, and transient noise analysis. PSS refers to periodic steady state, also known as Shooting Newton. HB refers to industry recognized Harmonic Balance.

- PLL Phase Noise – running transient noise for the closed loop PLL

In figure 5, below we can see all three methods of calculating phase noise for the VCO match very closely. In addition, the closed loop PLL phase noise also matches well with the three phase noise measurements of the VCO. This type of comparison can be achieved for many circuit types including switched-capacitor circuits, clocked comparators, and many others.

Siemens advances full-spectrum transient noise analysis to its third generation with SolidoTM Simulation Suite

The foundations and first generation of silicon accurate full-spectrum transient noise analysis were developed by Berkeley Design Automation (BDA) and enabled by directly solving the stochastic differential equations for noise, resulting in silicon correlation for ADCs and PLLs within 1-2 dB. Because of its high performance, capacity, and accuracy, it was selected as the sign-off solution for many leading semiconductor companies. This trend continued for smaller geometries down to 40nm in the planar FET nodes. Below 40nm, there was a disruption where the design complexity increased due to more sophisticated FET models, increased parasitics, lower voltages, and higher frequencies. However, upon entering the FinFET era (< 16nm), the complexity of the designs increased by 10x-100x as FinFET models were much more complex for analog simulators. It was no longer feasible to run pre-layout and estimated post-layout designs, resistance, and capacitance (RCC) extractions were required, which resulted in simulation runtimes 10x-20x longer for similar designs.

This trend forced a second generation of full-spectrum transient noise with the release of Analog FastSPICE eXTreme (AFS XT) in 2020. This technology addressed the new demands on circuit designers by maintaining accuracy with up to 10x performance boost over the original AFS implementation.

With the acceleration of process technology now pushing 2nm designs, FET models using Gate-All-Around are more complex, metal resistance has increased over 10x compared to 40nm, and simulation runtime increased by 20x. This has forced another step function to innovate and address designers’ needs for performance, capacity, while maintaining noise accuracy for the smallest geometries. Siemens advanced to its next and 3rd generation of full spectrum transient noise technology with Solido SPICE, part of the Solido Simulation Suite that was launched at Design Automation Conference 2024. Solido SPICE is Siemens’ next-generation, feature-rich SPICE simulation technology, providing a 2-30x speedup for analog, mixed-signal, RF and 3D IC verification. With newer convergence, cache efficient algorithms and high multi-core scalability, Solido SPICE provides a significant performance boost for large pre- or post-layout designs. RF IC developers can directly benefit from Solido SPICE’s new RF verification capabilities, while multi-die, 2.5D, 3D and memory interface developers can now experience an efficient capability for full channel transceiver verification that includes equalization, drastically reducing interface assumptions and accelerating verification.

Refer press release – Siemens introduces Solido Simulation Suite | Siemens Software

Summary

This article discusses the significance of full-spectrum transient noise analysis in the design of advanced analog and RF circuits, emphasizing its necessity for achieving silicon success. An introduction of noise in analog and RF circuits set the foundation for understanding device noise and how it is captured when running transient noise. Methods were shown to compare transient noise results to various RF methods achieving excellent correlation. We concluded with the progression through three generations of full-spectrum transient noise, ending in the most advanced implementation available in the Siemens’ Solido Simulation Suite.

Authors:

Scott Guyton – Director of Solutions Architecture, Custom IC Division

Pradeep Thiagarajan – Director of Product Management, Custom IC Division

Also Read:

Averting Hacks of PCIe® Transport using CMA/SPDM and Advanced Cryptographic Techniques

Reset Domain Crossing (RDC) Challenges

Electrical Rule Checking in PCB Tools

Share this post via: