A product launch nowadays demands shorter runway. SoC designers challenges are not so much in facing the unavailability of proven design capture methodologies or IP’s that could satisfy their product requirements, but more so in orchestrating the integration of all those components to deliver the targeted functionalities and performances.

A product launch nowadays demands shorter runway. SoC designers challenges are not so much in facing the unavailability of proven design capture methodologies or IP’s that could satisfy their product requirements, but more so in orchestrating the integration of all those components to deliver the targeted functionalities and performances.

While facilities for performing faster exploration by means of advanced modeling and prototyping during system architecture inception are widely accessible, shortening product development time requires scrutiny of long implementation processes. For example, high-level synthesis (HLS) has become mainstream and has provided a facility for exploration of system architecture configuration, power consumption, and design footprint versus feature tradeoffs. On the other hand, both functional and physical verification –which frequently dictate the success of the product launch, incur a late start due to the immaturity of most design blocks.

The motivation for early integration

With the plethora of AI and IoT oriented designs, the SoC integration efforts need to have an early start to align with a shorter product launch cycle. This translates to the need for having design methodology and point tools capable of providing early exploration and access to baseline metrics that highlight potential design integration issues.

With the plethora of AI and IoT oriented designs, the SoC integration efforts need to have an early start to align with a shorter product launch cycle. This translates to the need for having design methodology and point tools capable of providing early exploration and access to baseline metrics that highlight potential design integration issues.

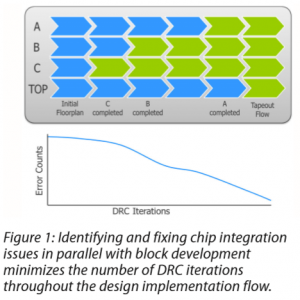

A common chip design approach is to have concurrent chip integration and block development to minimize the number of DRC iterations as illustrated in figure 1. The main challenge to early chip-level physical verification includes an artificially high number of reported DRC violations of the unfinished design blocks –which in major part attributed to the widespread occurrences of systematic issues such as off-grid placement; incorrect via type on a clock net; incorrect routing layer and orientation of IPs.

Additionally, it is also a complex task to segregate between block-level and top-level routing violations as topological changes (block-level pin to the top-level net), physical constraints (routing resources) and its associated DRC rules might introduce variants in the generated violations. Likewise, to use the default settings in foundry rule decks for initial DRC runs also leads to long runtimes, a massive number of DRC errors and large database.

Additionally, it is also a complex task to segregate between block-level and top-level routing violations as topological changes (block-level pin to the top-level net), physical constraints (routing resources) and its associated DRC rules might introduce variants in the generated violations. Likewise, to use the default settings in foundry rule decks for initial DRC runs also leads to long runtimes, a massive number of DRC errors and large database.

To enable design teams to start an early integration exploration while performing physical verification of their full-chip design layout, Mentor recently introduced Calibre™ Reconnaissance (in short, Calibre Recon). The tool is designated to effectively identify potential integration issues and generate quick feedback for corrective actions to the design teams, that eventually lead to lowering the DRC iterations and reducing physical verification time for tapeout closure.

In order to assess Calibre Recon effectiveness, we look into several areas: How it tackles with myriads of design rules while dealing with dirty designs? What about runtime? Physical verification notoriously incurs long turnaround time. How is it compared with the existing approach across designs?

Reduction in Rule Checks and Violations

Selecting relevant design rules is a daunting task as some rules may be important but may have long runtime in the presence of error. How does the designer know which ones to activate or to exclude? Which ones that will trigger advanced analysis? Indiscriminate selection of more categories such as antenna checks or all connectivity checks may also irrelevant for the current development phase and eventually produced sub-optimal results.

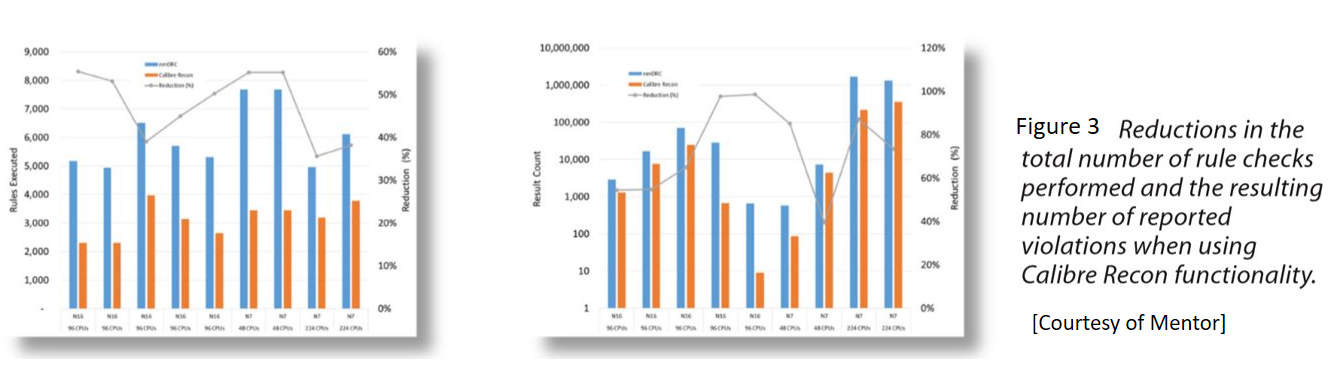

Calibre Recon automates the deselection process and decides based on the check type and the number of operations executed for the check. It aims for optimal coverage with quick runtime and less memory footprint. On average it cut the number of checks by half across various process nodes. The resulting deselection checks and categories are captured in the transcript for further reference. It honors the user’s manually pre-filtered checks/categories. As shown in figure 3, the total reports violations are reduced by as much as 70% of the original count and they facilitate the analysis and debugging of real systematic issues.

Calibre Recon automates the deselection process and decides based on the check type and the number of operations executed for the check. It aims for optimal coverage with quick runtime and less memory footprint. On average it cut the number of checks by half across various process nodes. The resulting deselection checks and categories are captured in the transcript for further reference. It honors the user’s manually pre-filtered checks/categories. As shown in figure 3, the total reports violations are reduced by as much as 70% of the original count and they facilitate the analysis and debugging of real systematic issues.

Runtime, Gray Boxing and nmDRC

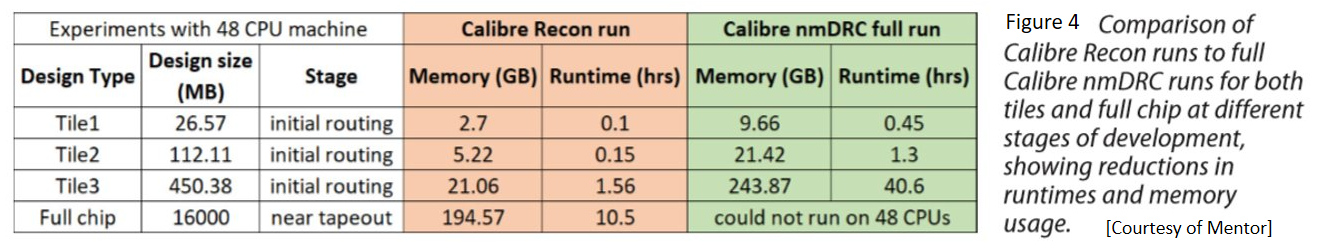

Calibre Recon supports both early block-level verification and chip-level validation as these two types of efforts are usually done in parallel by design teams. Having top-level context feedback from Calibre Recon allows block designer to fix systematic reported issues and provides more productive time for block designers to concurrently focus on cleaning up the remaining rules violations internal to their blocks.  As shown in figure 4, running the Calibre Recon tool on blocks (tiles) during initial routing resulted in up to 8x runtime improvement at 4x less memory.

As shown in figure 4, running the Calibre Recon tool on blocks (tiles) during initial routing resulted in up to 8x runtime improvement at 4x less memory.

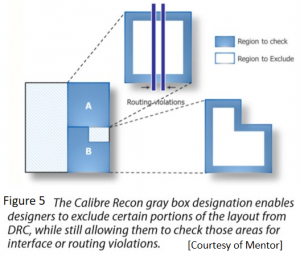

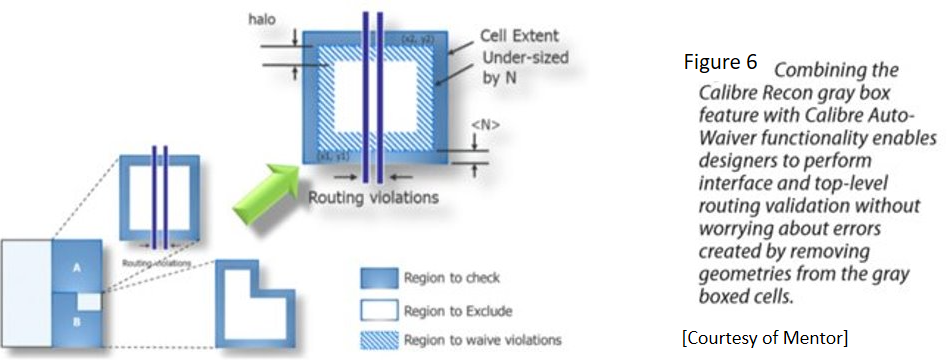

Another critical part of the integration work involves checking the consistencies of interfaces across design blocks and IP’s. An unfinished design block can be fitted into the top-level scope as a grey box to allow the designer to focus on interface and top-level routing checks while ignoring some internal block details. It allows topology-accurate inclusion of all design blocks or IPs at the top-level view and permits a more meaningful top-level floorplanning and timing assessment.

Another critical part of the integration work involves checking the consistencies of interfaces across design blocks and IP’s. An unfinished design block can be fitted into the top-level scope as a grey box to allow the designer to focus on interface and top-level routing checks while ignoring some internal block details. It allows topology-accurate inclusion of all design blocks or IPs at the top-level view and permits a more meaningful top-level floorplanning and timing assessment.

The gray box approach may optionally be used in conjunction with Calibre Auto-Waivers functionality. It helps in preventing new DRC violations due to removing geometries from the affected cells. This is achieved by waiving any violations introduced by excluding regions from the specified cells and all waived violations are saved to a waiver results database files for later review. The grey box solution isolates integration and routing violations associated with the assembly from the immature block violations.

Mentor Calibre Recon tool was proven to reduce the overall DRC runtime by up to 14x, while covers about 50% of the total DRC set. Its application during early integration accelerates the overall design recon and provides early design integration metrics for successful tapeout. For more details and chart of its application across a variety of chips, please check HERE.

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.