Analog design seems to suffer from a huge gap when it comes to testing and verification. While some of this gap is natural – after all, often the only way to verify whether a particular design is working is to look at actual simulation waveforms – it still seems like a lot can be done to bring process into this sphere of the IC design space.

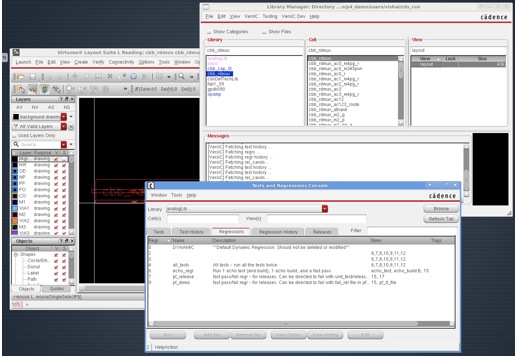

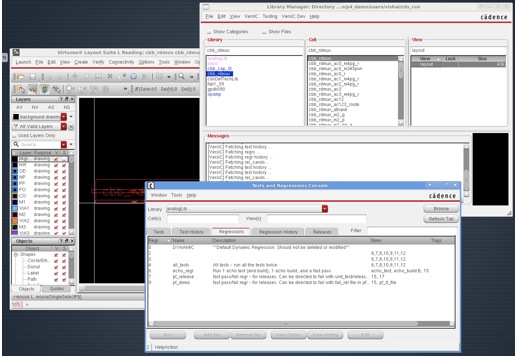

Analog designers generally work from their tool GUI’s. Even if they could run automated, or scripted tests to check those parts of the design that don’t need human intervention or bringing up waveforms, it is often hard to get the team to run these tests since they need to be launched from a terminal. In addition, test results are not available from within the GUI.

From a management perspective, analog designs are getting larger, more complex and distributed. One small mistake can cost millions in respins and lost market window. Enabling seamless collaboration across the globe, and tracking team progress is a challenge.

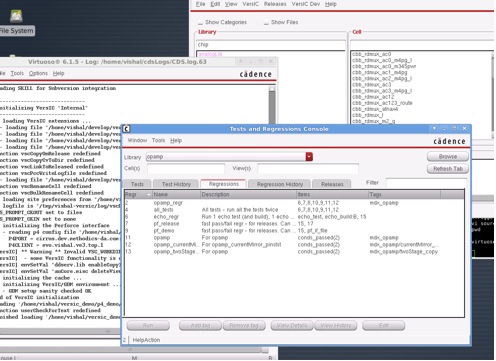

Analog Verification can now be automated using a management console as a new way of looking at testing in the analog/mixed signal design context. A company called Methodics offers a Data Management tool called VersIC with a plugin for Analog Verification management. This plugin for VersIC works in the Cadence Virtuoso 5.x/6.x environments and with the Synopsys Custom Design tools.

Analog IC designers create wrapper scripts to run their ADEXL/ADE/Ocean tests and then use the plugin GUI to register the script and define its required arguments. This is captured in the VersIC database and made available to the entire team

Verification tests can be combined into regression suites, making it easy to run and track a slew of related tests as a single entity. The tool understands all the popular grid management software, so regressions can be launched in parallel, dramatically cutting testing time.

Analog Tests

An analog designer can now automate and keep track of LVS, DRC, power consumption bounds, jitter and leakage measurements. Any kind of ADEXL/Ocean scripted test is a good candidate for this approach. VersIC with the plugin is quite simple to use. Most engineers are up and running in a couple of hours after reading the documentation examples or meeting with a knowledgeable AE.

The alternative to automating analog verification are manual efforts with spread-sheets or writing your own scripts. Using something off the shelf to automate analog tests saves time and lets you concentrate on your core design competence.

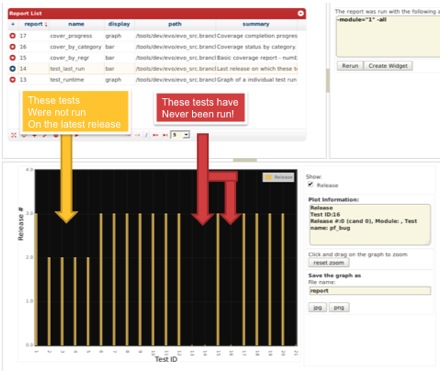

VersIC’s SQL database tracks all the tests run across the team – across multiple sites, multiple workspaces, multiple users – making for very effective collaboration.

Now, with a single click, managers can track all the tests run, across their entire team on a given release of a design. You can look at pass/fail rates of individual tests, and even figure out all the design changes that have happened since the last time a particular test passed.

History

The VersIC tool was first released in 2007 and is being used by a mix of large and small companies including: Cisco, Broadcom, PMC Sierra, Motorola, Cirrus Logic, Google, Wolfson, Lantiq, Huawei and ZMD.

Other vendors don’t offer a data management solution with releases attached to a database of the entire test history for that release. In mixed-signal designs this can be combined with the Evolve digital solution from Methodics allowing a single release mechanism for all analog/digital design data with the corresponding verification history.

Summary

Management always has the issue of “what tests have been run and did they all pass” whenever a major release is under consideration. Often “minor” changes to a schematic or layout are included in a release without being properly verified and cause expensive rework. With VersIC’s Analog Verification Management tools, this uncertainty can be removed and design teams can release with confidence, saving hours of manual work per week and helping ensure that silicon is correct.

lang: en_US

Share this post via:

Comments

0 Replies to “Analog IC Verification – A Different Approach”

You must register or log in to view/post comments.