I read about how Toumaz used the Analog Fast SPICE (AFS) tool from BDA and it sounded interesting so I setup a Skype call with Alan Wong in the UK last month to find out how they design their ultra low-power IC chips.

Interview

Q: Tell me about your IC design background.

A: I’ve been at Toumaz almost 8 years now and before that at Sony Semi for 5.5 years. My IC design experience goes back to 1997, then starting in 2005 I’ve been in the IC design group for wireless.

Q: Does Toumaz have a CAD group?

A: Yes, we do have two CAD engineers.

Q: What EDA tools are you using?

A: For RTL simulation we have Mentor Questa, and on physical verification we’re using Calibre. Place & Route it’s Synopsys and for IC layout we’ve got Cadence Virtuoso and Assura (verification). Circuit simulation we have the Analog Fast SPICE tool from Berkeley Design Automation.

Q: How about your product life cycle?

A: Most of our IC designs go from definition to Tape out in about 18 months, some are quicker. Foundry choices have been: TSMC, IBM, Infineon, UMC.

Q: What’s the first thing that you do when silicon comes back from the fab?

A: With our engineering samples we first test to see if our spec is met, then we start to characterize with initial functional vectors plus the specialized analog RF testing.

Q: For circuit simulation tools, what have you used before?

A: We’ve used Cadence Spectre tools before, then we switched over to BDA. We found better results with the Berkeley tool in terms of speed. In our evaluation we used internal designs, multiple test benches and clock circuits, taking several weeks to complete our benchmarking. Overall we saw, about 5X quicker with AFS.

Q: When the foundry provides SPICE models have there been any issues?

Q: Yes, we had some issues with model cards and BDA. There were some differences between Spectre and BDA, causing BDA to make some tweaks in their BSIM4 RF models.

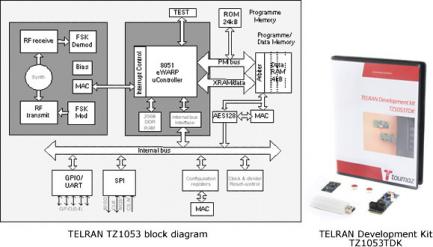

Q: How do you simulate the whole mixed-signal chip?

A: For Mixed-signal chips we model at two levels of abstraction, behavioral and transistor level. During simulation we can swap out transistor level versus behavioral to get the speed and accuracy trade-off we need. For analog blocks we simulate at the transistor level.

Q: Why not use a Fast SPICE simulator for full-chip circuit simulation?

A: Our experience shows that Full-chip with Fast SPICE gives fast but wrong answers.

Q: Which process nodes are you designing at?

A: Quite a range: 130nm and 110nm, some 65nm nodes.

Q: How large are your design teams?

A: Our design team for an SOC uses a Personal Area Network and has some layout designers, firmware team, test and production engineers, maybe 20 people in total.

Q: What is your version control system?

A: We have used SVN for just the RTL coding side and also tried the Design Management Framework within Cadence IC 5. Our plan is to start using ClioSoft soon in Cadence IC 6.

Q: Are there other circuit simulation tools that you’ve looked at?

A: Quite a few: Synopsys, Aglient and Golden Gate.

Q: What’s really important for your circuit simulations?

A: Accuracy and the ability to do long simulation runs, some are up to one week in duration. We do some top level parametric simulation, try different scenarios, and run lots of configurations.

Q: What needs improvement for your circuit simulation?

A: Well, there’s some room for improvement with co-simulation, it can be a bit flakey. We co-simulate with Verilog.

Q: How often does BDA update their software?

A: With BDA there are updates every few months, so we just wait for the new features that we need then install it about once a quarter.

Q: What about your layout tools from Cadence?

A: We freeze the Cadence toolset at the start of each project and update tools only if really needed during a project.

Q: What was the learning curve for the BDA circuit simulator?

A: The learning curve was short for us, we now know how to setup the options to get the accuracy vs speed.

Q: What’s your wish list for BDA?

A: I would prefer more flexible license terms throughout the year (like Cadence credits). We always want circuit simulation to be Faster, more accurate, and improved DC convergence.

Summary

Toumaz uses a mixture of EDA tools to design their ultra low-power IC designs, working with vendors like: Berkeley Design Automation, Cadence, Mentor Graphics, Synopsys and ClioSoft.

Silicon Insurance: Why eFPGA is Cheaper Than a Respin — and Why It Matters in the Intel 18A Era