I spent Thursday Sept. 22 at the first nanometer Circuit Verification Forum, held at TechMart in Santa Clara. Hosted by Berkeley Design Automation (BDA), the forum was attended by 100+ people, with circuit designers dominating. I spoke with many attendees. They were seeking solutions to the hugely challenging problems they are wrestling with today when verifying high-speed and high-performance analog and mixed-signal circuits on advanced nanometer process geometries.

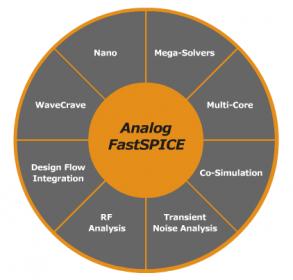

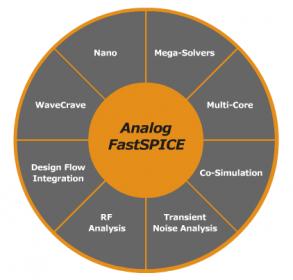

One critical need is for very accurate circuit simulation that can precisely model the underlying physical nanometer effects with very fast simulation run-times. BDA claimed that its Analog FastSPICE (AFS) delivers this today, with foundry sign-off accuracy and the industry’s only silicon-accurate device noise analysis. All of this, and the world’s fastest nanometer circuit verification. Can it be true?

According to the presenters at the forum, the answer is a resounding and definite yes. Attendees saw 15 user-presented experiences, drawn from active customers, university researchers, and EDA partners, all describing in detail how Analog FastSPICE delivers performance from 5X to 30X faster than other “golden” circuit simulators. In many cases this saves weeks or even months of simulation time and makes efficient circuit verification that has never been possible – or even attempted – before. There were several cases where AFS was “only” 2x-3x faster than “golden” SPICE simulator, but all of these were small circuits (e.g., <1K transistors) with short runtimes (e.g., a few minutes).

Presenters from industry and universities described how AFS is used to verify data converters (both over-sampled and Nyquist) and closed-loop PLLs to within 1 or 2dB of silicon characterization. A broad range of additional circuits was also presented, from VCOs to entire top-level SerDes circuits (including two PLLs, one for clock and data recovery and one for transmit clock generation). New verification methodologies were also described; for example, the use of variable domain translators to perform linear AC analysis in non-voltage domains, allowing DLL/PLL delay and phase transfer function to be easily computed, as well as supply noise impact on delay and phase, and DLL/PLL bandwidth.

EDA partners Accelicon, Ciranova, Invarian, MunEDA, and Solido, presented their own unique nanometer-focused solutions, each containing BDA’s AFS at its core. They each gave demonstrations to attendees over a reception at the end of the day.

The agenda was rounded out with a keynote address from industry luminary Jim Hogan, covering highlights from his extensive career in semiconductor and EDA, and looking forward to some key future challenges. In summary, the nanometer Circuit Verification Forum was, I believe, a great success. I’ll leave you all with a remark from Jim Hogan’s keynote:

“the changing scale of physics has always created new opportunities for algorithmic and numerical techniques. Circuit simulation is now back – it’s where the action is.”

I couldn’t agree more. Great FREE lunch too! Yes I blog for food.

* Note: You must be logged in to read or write comments

Musk’s Orbital Compute Vision: TERAFAB and the End of the Terrestrial Data Center