One of the more entertaining things I get to observe in the semiconductor ecosystem is competitive customer evaluations of tools and IP. Seriously, this is where the rubber meets the road no matter what the press releases say.

One of the more entertaining things I get to observe in the semiconductor ecosystem is competitive customer evaluations of tools and IP. Seriously, this is where the rubber meets the road no matter what the press releases say.

This time it was emulators which is one of the most interesting EDA market segments since there is no dominant vendor. So it really is three big dogs eating out of one bowl as former Cadence CEO Joe Costello so elegantly put it many years ago. We all know Mentor dominates verification, Cadence AMS design, and Synopsys Synthesis and IP. But for emulation Mentor, Cadence, and Synopsys all have sizable dogs at this $300M+ bowl.

In my experience with emulation evaluations, if there is an incumbent (an already installed system) they have a distinct advantage, unless of course the customer has “outgrown” them which is what happened in this case. I had the inside track since I know Wave and have been waiting patiently for the press release to blog it:

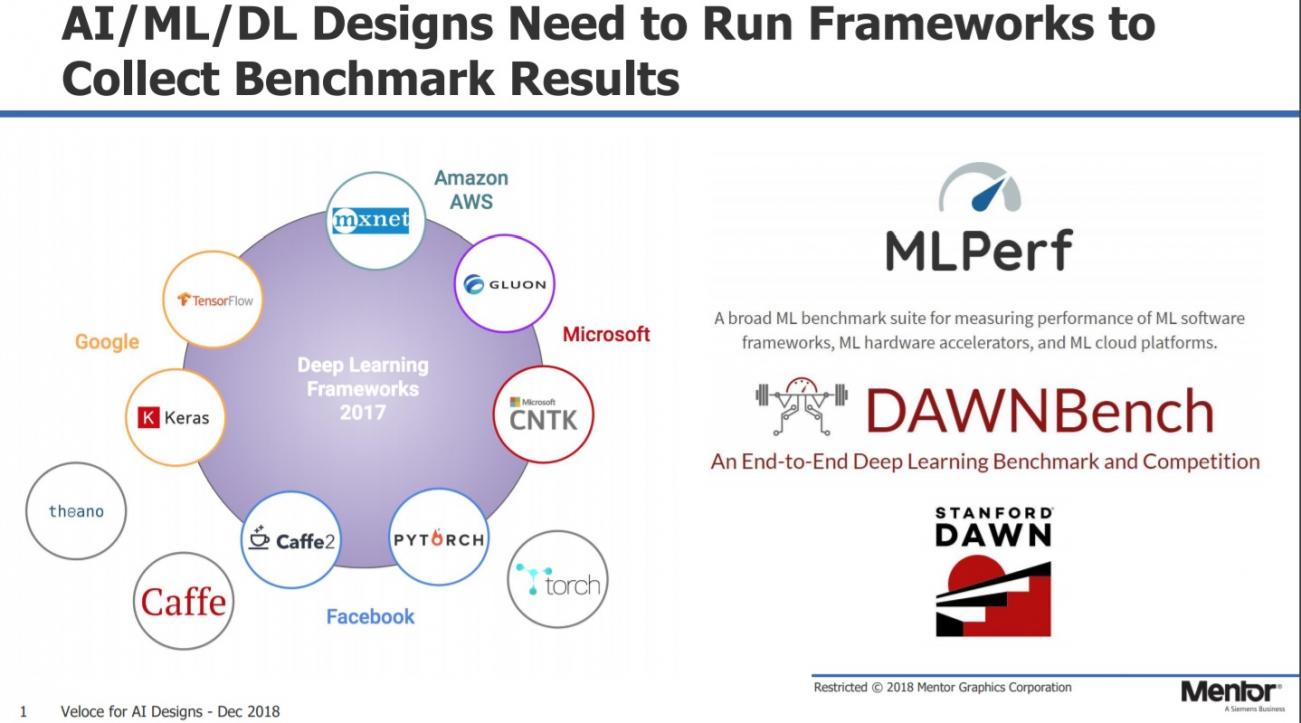

“Wave Computing is revolutionizing artificial intelligence and deep learning with our dataflow technology-based solutions, which are pushing the boundaries of AI system design. The Veloce Strato roadmap not only addresses growing capacity needs, but it also maps to the diverse and expanding challenges of hardware/software verification and validation,” said Darren Jones, vice president of Engineering, Wave Computing. “When we saw that our reliance on hardware emulation was growing beyond early software validation, we evaluated all available tools. The Veloce Strato platform was the best solution that met our needs. It enables a robust virtual emulation environment that tackles complex AI design challenges.”

“Wave Computing is revolutionizing artificial intelligence and deep learning with our dataflow technology-based solutions, which are pushing the boundaries of AI system design. The Veloce Strato roadmap not only addresses growing capacity needs, but it also maps to the diverse and expanding challenges of hardware/software verification and validation,” said Darren Jones, vice president of Engineering, Wave Computing. “When we saw that our reliance on hardware emulation was growing beyond early software validation, we evaluated all available tools. The Veloce Strato platform was the best solution that met our needs. It enables a robust virtual emulation environment that tackles complex AI design challenges.”

Coincidentally I was interviewed by CNBC last week and asked why smart phone companies are making their own SoCs instead of just buying them from Qualcomm. One of the reasons of course is emulation. When you design an SoC you can quickly debug the chip on an emulator then get started with software development before the silicon is back. Bigly advantage for a company like Apple who has lots of software floating around their SoCs, absolutely.

After talking to Jean-Marie Brunet, Director of Marketing, Emulation Division at Mentor Graphics, and getting some slides, I sent some questions to Darren Jones and Edmund Jordan at Wave:

Q: I would like to know why you chose Mentor?

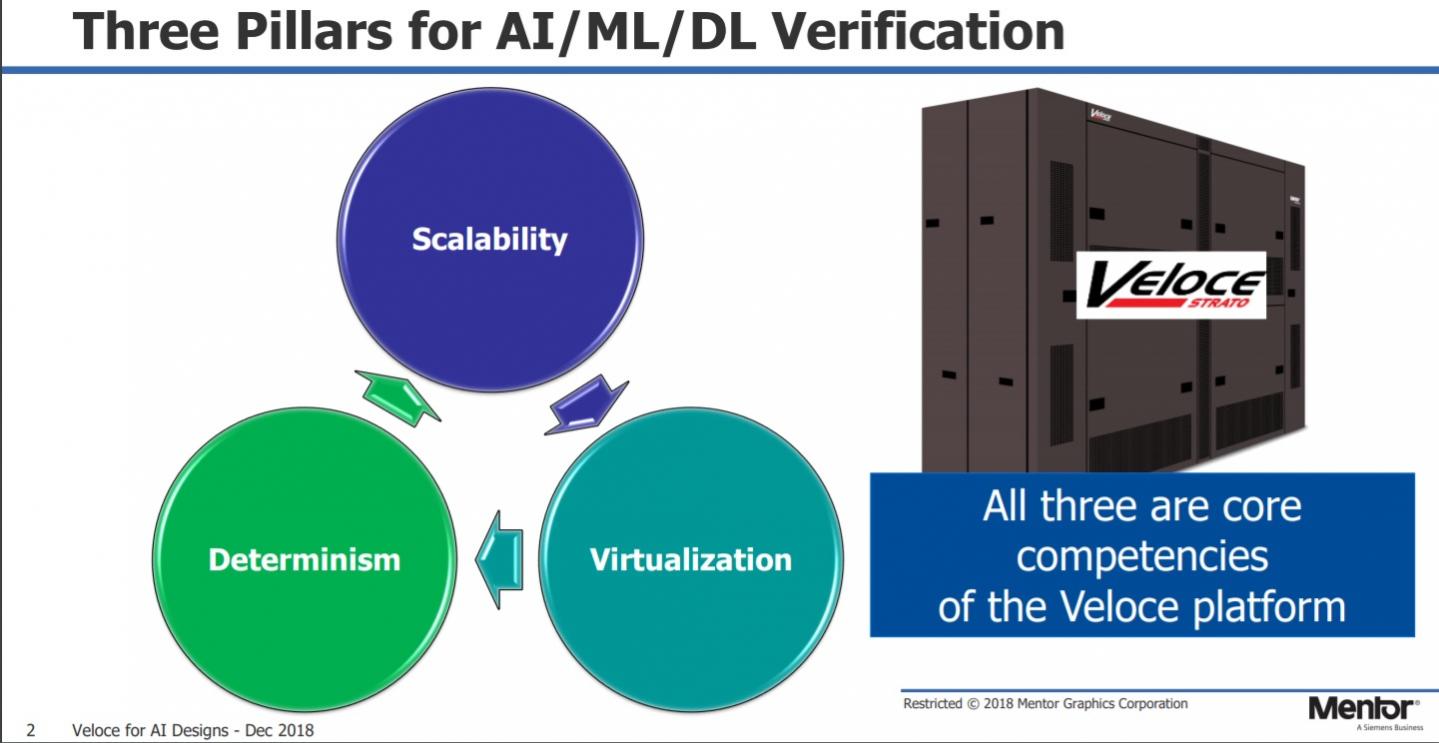

We selected Mentor because the platform performed debugging processes far better, which is where we were spending the majority of our time. By helping us significantly reduce the amount of time we spent debugging, Mentor helped us speed time-to-market. Mentor’s Veloce® Strato™ emulation platform also included several different interface options and other features which led to Veloce being a far more complete solution, out-of-the-box.

Q: Can you elaborate on the details of your design?

We have a rather large design within a leading-edge process node. As is industry standard, we believe emulation is a key part of verifying design before the proposed solution is put on silicon, which is why we turned to Mentor’s Veloce® Strato™ emulation platform for assistance. Our design includes memory interfaces such as DDR, PCIE cards, etc. as well as a large array of custom processors.

Q: How fast did your design run on the emulator?

A rough estimate would be that we run about 1MHz, which is a notable improvement over what we ran on our previous product when debug is enabled. However, we use the emulator primarily for debugging the design so absolute speed is not as important as the speed of debugging.

Q: What is your chip design methodology?

We primarily use standard Verilog RTL, Synthesis, and place and route design methodologies. We do use custom blocks when performance is required.

Q: Is the chip taped out?

Yes.

Q: First silicon working?

Yes.

Q: Anything else interesting to add?

One advantage—and one of the reasons we chose Veloce—is that it’s very easy to use for hardware debug when running real-world software applications. What we liked most is that we could run different simulation cycles without having to recompile the design. This helps speed our development cycles, which is certainly advantageous.

We’ll always have simulation, but the advantage of emulation is it’s much faster than simulation. Thus, it enables us to run software that would take too long to run on a simulator. However, I’m certainly not going to run every software scenario on an emulator because doing so is not cost effective.

If you want to know who the incumbent was you will have to login and read the comments…

Share this post via:

Comments

There are no comments yet.

You must register or log in to view/post comments.